### Tesi di Dottorato

Università degli Studi di Napoli "Federico II"

DIPARTIMENTO DI INGEGNERIA ELETTRICA E TECNOLOGIE DELL'INFORMAZIONE

DOTTORATO DI RICERCA IN INFORMATION TECHNOLOGY AND ELECTRICAL ENGINEERING

# CRYPTOGRAPHIC EXTENSIONS FOR CUSTOM AND GPU-LIKE ARCHITECTURES

### Domenico Argenziano

Il Coordinatore del Corso di Dottorato Il Tutore

Ch.mo Prof. Daniele RICCIO Ch.mo Prof. Alessandro CILARDO

A. A. 2016–2017

"To my parents, to my sister and my family, to my friends and to Erminia, as well."

### Acknowledgments

First, I want to express my sincere gratitude to...

my tutor Alessandro Cilardo, for his great patience with me, my colleagues Mirko Gagliardi and Innocenzo Mungiello for their helpfulness, my temporary co-tutor Clemente Galdi for his invaluable contribution, Flemming Christensen for having allowed me to make an interesting abroad experience.

## Contents

| A  | ckno                  | wledgr | nents                                           | v  |

|----|-----------------------|--------|-------------------------------------------------|----|

| Li | st of                 | Figur  | es                                              | ix |

| In | $\operatorname{trod}$ | uction |                                                 | xi |

| 1  | Cus                   | stom a | ccelerator for homomorphic encryption           | 1  |

|    | 1.1                   | Applie | cations                                         | 2  |

|    | 1.2                   | Backg  | round                                           | 5  |

|    |                       | 1.2.1  | Mathematical background                         | 5  |

|    |                       | 1.2.2  | Previous works                                  | 15 |

|    | 1.3                   | Appro  | each followed                                   | 16 |

|    | 1.4                   | Archit | tecture of the FPGA-based accelerator           | 22 |

|    |                       | 1.4.1  | Data distribution and exchange pattern          | 25 |

|    |                       | 1.4.2  | FFT-64 unit                                     | 26 |

|    |                       | 1.4.3  | Internal Bank Memory                            | 29 |

|    |                       | 1.4.4  | Modular multiplier                              | 30 |

|    |                       | 1.4.5  | Data route                                      | 30 |

|    | 1.5                   | Imple  | mentation and performance                       | 31 |

| 2  | GP                    | U exte | ension for Montgomery Multiplication            | 33 |

|    | 2.1                   | Modu   | lar Multiplication                              | 33 |

|    |                       | 2.1.1  | Montgomery modular reduction and multiplication | 33 |

|    |                       | 2.1.2  | Barrett modular multiplication                  | 35 |

|    |                       | 2.1.3  | Camparison with Montgomery reduction            | 35 |

|    | 2.2                   | Previo | ous works                                       | 37 |

|    | 2.3                   | From   | the algorithm to the GPU-like datapath          | 38 |

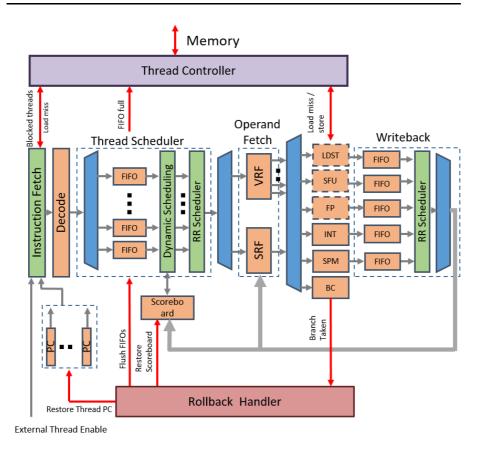

|    |                       | 2.3.1  | The $Nu+$ GP-GPU datapath                       | 38 |

|    |                       | 2.3.2  | Algorithm GPU-ization                           | 43 |

viii CONTENTS

|    |               | 0.2.2  | D-t- dddd                                            | 40 |

|----|---------------|--------|------------------------------------------------------|----|

|    |               | 2.3.3  | Data dependencies and access patterns                |    |

|    |               | 2.3.4  | Data movement and bandwidth                          |    |

|    |               | 2.3.5  | Width and number of lanes                            |    |

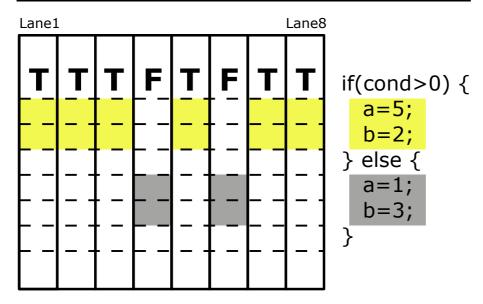

|    |               | 2.3.6  | Predicated execution                                 | 50 |

|    |               | 2.3.7  | Integration of the Montgomery unit                   | 50 |

|    |               | 2.3.8  | Definition of an extended Instruction Set            | 51 |

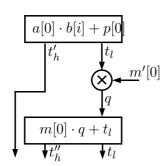

|    | 2.4           | Detail | s of the Montgomery functional unit                  | 51 |

|    |               | 2.4.1  | Data arrangement                                     | 51 |

|    |               | 2.4.2  | Carry-less multiplication                            | 52 |

|    |               | 2.4.3  | Carry recovery and final subtraction $\dots \dots$ . | 53 |

| 3  | $\mathbf{AE}$ | Sexte  | nsions for GPU                                       | 57 |

|    | 3.1           | Algori | $\operatorname{ithm}$                                | 57 |

|    | 3.2           | Archit | tecture                                              | 58 |

|    |               | 3.2.1  | Resource-friendly implementation                     | 58 |

|    |               | 3.2.2  | Optimizations                                        |    |

|    |               | 3.2.3  | Dedicated HW implementation                          |    |

|    |               | 3.2.4  | Inverse cipher                                       |    |

| 4  | Ext           | erime  | ntal results                                         | 65 |

|    | 4.1           |        | gomery multiplication                                | 65 |

|    | 4.2           |        | 128 encyption                                        |    |

| Co | oncli         | ısion  |                                                      | 69 |

## List of Figures

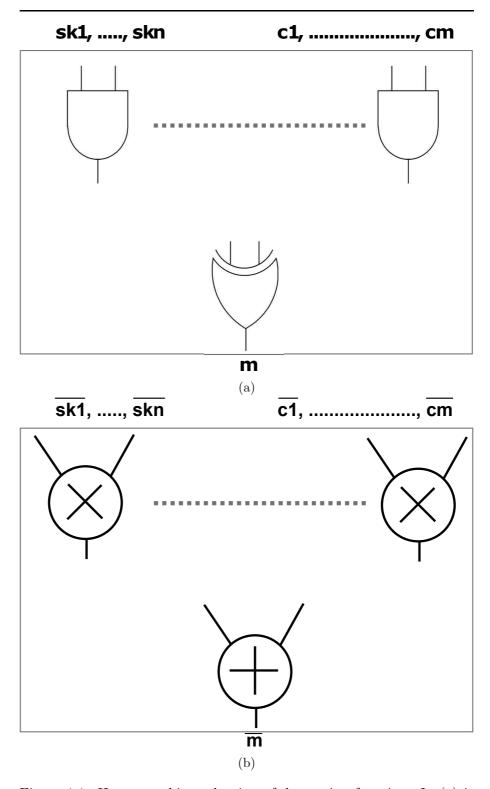

| 1.1  | Homomorphic evaluation of decryption function. In (a) is<br>presented the original boolean function, while in (b) the<br>corresponding arithmetic function evalued on the cipher- |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | texts                                                                                                                                                                             |

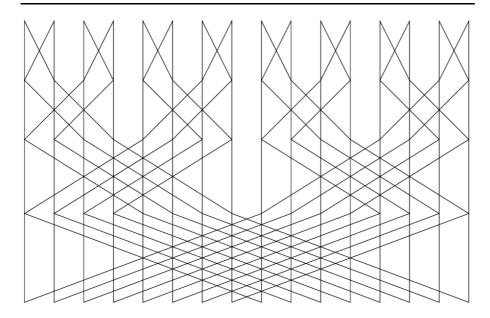

| 1.2  | Butterfly scheme of the Radix-2 FFT                                                                                                                                               |

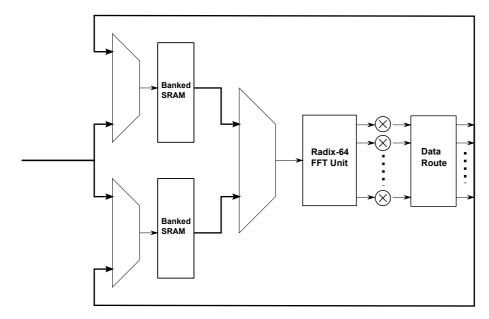

| 1.3  | Architecture of a 64K FFT processing element                                                                                                                                      |

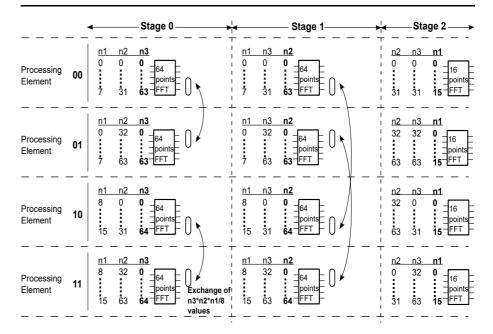

| 1.4  | Data distribution                                                                                                                                                                 |

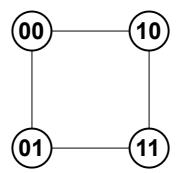

| 1.5  | Hypercube topology for a system comprising four Pro-                                                                                                                              |

|      | cessing Elements                                                                                                                                                                  |

| 1.6  | Hypercube topology for a system comprising eight Pro-                                                                                                                             |

|      | cessing Elements                                                                                                                                                                  |

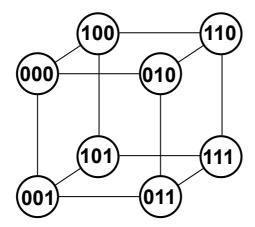

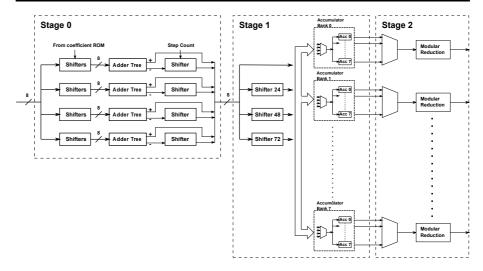

| 1.7  | Architecture of the baseline Radix-64 unit [1] 26                                                                                                                                 |

| 1.8  | Architecture of FFT64 unit                                                                                                                                                        |

| 1.9  | Architecture of banked memory buffer                                                                                                                                              |

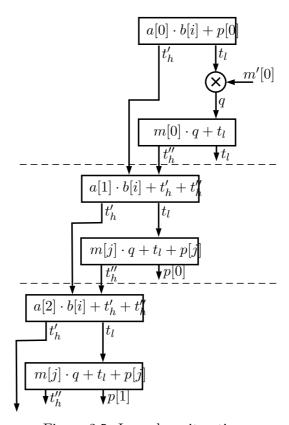

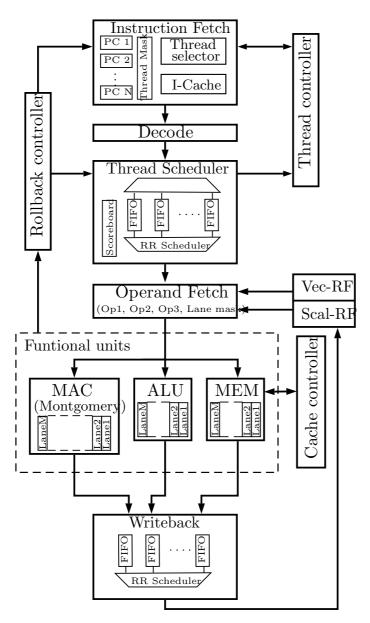

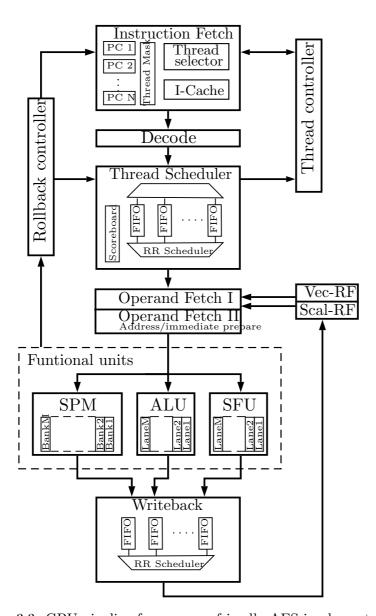

| 2.1  | Overall view of $Nu+$ datapath                                                                                                                                                    |

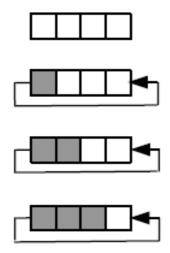

| 2.2  | Predicated execution using masks                                                                                                                                                  |

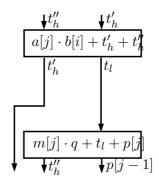

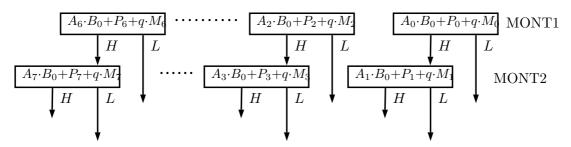

| 2.3  | Inner loop: first iteration                                                                                                                                                       |

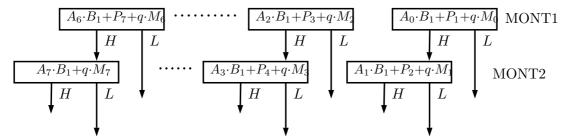

| 2.4  | Inner loop: other iterations                                                                                                                                                      |

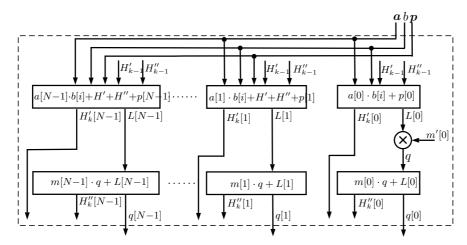

| 2.5  | Inner loop iterations                                                                                                                                                             |

| 2.6  | GPU-like pipeline. Only the functional units of interest                                                                                                                          |

|      | are shown                                                                                                                                                                         |

| 2.7  | Montgomery unit architecture                                                                                                                                                      |

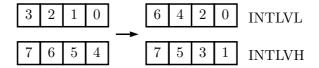

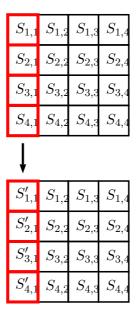

| 2.8  | Data interleaving using INTLVL and INTLVH instruc-                                                                                                                                |

|      | tions (case of operands occupying two registers) 52                                                                                                                               |

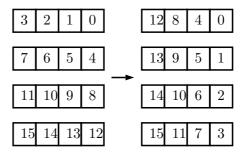

| 2.9  | Data interleaving using INTLVL and INTLVH instruc-                                                                                                                                |

|      | tions (case of operands occupying four registers)                                                                                                                                 |

| 2.10 | First iteration of carry less multiplication                                                                                                                                      |

| 2.11 | Second iteration of carry less multiplication                                                                                                                                     |

| 3.1 | Row rotate                                            | 61 |

|-----|-------------------------------------------------------|----|

| 3.2 | Column mixing stage                                   | 62 |

| 3.3 | GPU pipeline for resource-friendly AES implementation | 63 |

### Introduction

The need for information security has increasily become a serious concern in the era of widespread digitalization, mobile networking and Cloud-based services. Even bigger concerns have arisen since Cloud computing and Big Data paradigms for storing, processing and manipulating digital data have achieved wide diffusion on a large scale and a large class of distributed applications over the past two decades. Traditional security techniques have focused mostly on the storage and transport of information, e.g. by encrypting files, authenticating servers and setting up secure channels. In Cloud computing scenario, even these techniques are starting to appear insufficient, since the peculiar aspect of Cloud computing is outsourcing data storage and computation to a third-party remote resource provider, which, in turn, will allocate programs and data over a large network of machines, with little to no control by data owners. Certainly, data can be stored and transmitted in encypted form, but if it has to be processed, then data should be in unencrypted form. In this case, the customer must trust the Cloud service provider not to leak, maliciously or unintentionally, confidential data while also preserving data integrity against illicit manipulations. The ideal solution would be a tecnique which would allow to carry out computation on encrypted data. This, which could seem like an impossible task, can be actually achieved using homomorphic encryption, which actually allows computation to take place on encrypted data on the server side. While existing encryption schemes, such as RSA, were already known to be at least partially homomorphic, it is only with the seminal work of Craig Gentry in 2009 that a fully homomorphic scheme was finally devised. An alternate technique is that of Yao's Garbled Circuits [2] and all derived techniques, also including hybrid approaches. Unfortunately, these schemes come with a prohibitively high computational cost which prevents them to be practically used in any real scexii Introduction

nario. Nonetheless, noticeble progresses have been accomplished from the algorithmic point of view, reducing time complexity and, hopefully, further improvements may come in the future, which will make homomorphic encryption more practical. Even in that case, software and hardware optimization techniques are still needed in order to make its implementation feasible.

When we consider more standard cryptographic primitives, their computational cost, even though more reasonable, can still be quite high, especially in the case of public key cryptography. Such cost is often regarded as an undesired overhead, since some computing resources have to be taken away from *useful* tasks. Indeed, serious security protocols for Internet were adopted well after Internet itself widespread diffusion, when security threats had already became a major concern.

This thesis work will deal with the exploration of acceleration solutions for cryptographic operations, both those more advanced, such as homomorphic encryption, that more standard ones, such as AES for symmetric key cryptography and RSA and Elliptic Curves for public key cryptography. Given the peculiar nature of cryptographic operations, it is usually agreed that some kind of hardware acceleration is usually needed, since it can yields far better performances that software-only approaches based on commodity processors. Indeed, most security libraries (e.g. OpenSSL) tries to exploit special extensions, such as SIMD instructions, present on commercial CPUs, like Intel AVX.

Current trends in computing architectures offer a variety of solutions for acceleration, ranging from general-purpose multi/many-core processors to Graphics Processing Units (GPUs) and Field-Programmable Gate Arrays (FPGAs).

FPGAs have a large potential for security-related processing and have proved to be an effective platform for cryptographic processing [3] as cryptoalgorithms have peculiar characteristics, like integer computation, bit-level manipulation, etc., that make standard platforms like CPUs and GPUs less competitive. On the other hand, hardware reconfigurability allows the designer to customize the system possibly based on specific parameters, e.g. a cryptographic key, making FPGAs an ideal platform for cryptographic acceleration [4, 5, 6] as well as for cryptanalytic purposes [7, 8, 9]. FPGA platforms have also been explored as a secure compute/storage environment [10, 11, 12] as well as for implementing special security-related features like Physically Unclonable

**Introduction** xiii

Functions [13].

The thesis presents the results achieved for the acceleration of operations essential to homomorphic cryptography, specifically, the integer multiplication of very long operands, based on the Schonhage-Strassen algorithm and implemented with an ad-hoc FPGA hardware. Then, we report the exploration of novelty approaches for cryptographic acceleration, based on vectorial dedicated architectures, such as General Purpose GPU, which are software programmable, with the corresponding implementation of symmetric and public key algorithms (namely, AES encryption and Montgomery multiplication) exploting dedicated units for improved performances.

The outline of the thesis is the following:

Chapter 1 presents the design of a custom accelerator for homomorphic encryption. More specifically, such accelerator is intended to perform high order number theoretic FFT, which is the main building block for very long operand multiplication. Such multiplication is the common bottleneck of homomorphic encryption schemes.

Chapter 2 describes an implementation of the Montgomery multiplication algorithm, widely used in common asymmetric schemes (such as RSA) based on the extension of a GPU-like core with special function units, exporting such new functionalities through an extended ISA which allowed to rewrote the original algorithm exploiting the hardware acceleration.

Chapter 3 describes extensions for a GPU-like core in order to accelerate AES-128 symmetric encryption. Two versions of the algorithm implementation are reported, the first which tries to exploit the Scrathpad memory already present in the core, the latter using completely ad hoc units, in order to achieve the best performances.

**Chapter 4** reports the experimental results for the solutions presented in Chapter 2 and Chapter 3.

### Chapter 1

## Custom accelerator for homomorphic encryption

or storing and processing heterogeneous data, Cloud computing environment [14, 15, 16] has posed serious problems from the point of view of security, since data confidentiality on a remote server cannot be reliably verified by the customer. This is not a concern when only the transmission or storage of data is taken into consideration, since it can be well protected using several cryptographic techniques. Specifically, symmetric key cryptosystems are usually used to ensure data confidentiality, while public key ones can satisfy integrity and authenticity requirements. This cannot be immediately applied in the case of executions of programs on confidential data, since such data cannot be encrypted. Therefore, in such case, the customer would have no choice but to trust the service provider not to violate data confidentiality nor to illicitly manipulate such data.

A promising answer to this concern may come from homomorphic encryption (HE). Introduced in its full form by the seminal work by Craig Gentry [17] just a few years ago, this sophisticated cryptographic technique allows arbitrary computation to take place on encrypted data, with little chance for the server performing the computation of accessing user data in plain form. Beside Gentry's scheme, based on the properties of ideal lattices, various alternative solutions have been proposed, the most relevant being the van Dijk, Gentry, Halevi and Vaikuntanathan's (DGHV) scheme over the integers, and the Brakerski and

Vaikuntanathan's scheme [18] based on the Learning with Errors (LWE) and Ring Learning with Errors (RLWE) problems [19]. While in their current instantiations homomorphic primitives handle information and operation at a very low level, i.e. at the bit level, in a perspective scenario HE can act as an enabling tool for a number of different applications, including multiparty computation, where several parties process a common, public function on their inputs while keeping their individual inputs private, medical applications, allowing patient records to remain confidential while being processed in the cloud; financial applications, electronic voting, etc. Despite its great potential, however, homomorphic encryption suffers from a high computational cost, both in terms of time and memory occupancy, which currently prevents its practical use.

In that respect, as implied by our introductory comment, the availability of dedicated FPGA-based acceleration in server settings might play a key role. Motivated by both the security challenges and emerging compute technologies of today's cloud scenarios, this chapter we present the architecture and FPGA-based implementation of a dedicated hardware accelerator addressing the prohibitive computing demand of homomorphic encryption. In particular, this chapter will describe a highly customized FPGA accelerator implementing ultralong-integer multiplication, the main performance bottleneck in most homomorphic encryption schemes. In the following, we'll present an implementation based on an Altera's Stratix V FPGA platform. The experimental results collected from the hardware synthesis show significant improvements in terms of execution time –under comparable hardware cost– against alternative solutions previously presented in the technical literature.

### 1.1 Applications

Before dwelling in the technical details of both homomorphic encryption and our proposed accelerator, we will briefly review some use cases which can greatly benefit from the use of such cryptographic system.

**Delegation of computation** This is the most immediate and obvious use case for homomorphic encryption. Nowadays, several possible delegation scenarios have emerged, ranging from the provisioning of virtual machines and platforms to remote data storage and applications, such

as Google Apps. All these kinds of services share the risk of being physically located outside the control of the customer. Using homomorphic encryption, the customer sends to the service provider an encrypted version of his software and data. The code included in the customer package is then executed on the remote server in encrypted form and when its execution is completed, the encrypted results are sent back to the customer, who retrieves the plaintext result by decrypting with the secret key.

Secret Query Evaluation If a company needs to store a database using a Cloud service, it has to trust such service provider both for the privacy of database content itself and of the queries the customer is going to perform on that database. That is, the service provider, not only has access to the database as a plaintext, but it can also log any customer query, with detail about the specific search and its time. While it is possible, with conventional cryptography, to hide the query and its result from an external adversary by using authentication and secure channels. Nonetheless, in some scenario, the customer may want to hide the query and its result from the Cloud provider itself and, optionally, he may wish to hide the content of the database itself. An example of the first situation is a classic Google query, where the searched database is obviously not private but the user may desire to hide the content (and results) of his/her search. An example of the second case is when the database contain medical record, which are sensitive data and are therefore better stored encrypted.

Medical records private access This scenario represents the most strict version of the one in the previous paragraph. Patient records should be stored in encrypted form given the sensitive nature of such data. Homomorphic encryption can allow to perform queries on the database in encrypted form, with result decrypted by the user once it has been received. Users are usually medically doctors, that may wish to access records remotely, for diagnosis, monitoring and other tasks. Additionally, it should be possible for patients to control which persons he wants to share his medical history with.

Mobile Agents Using an homomorphic cryptosystem in order to protect mobile agents can be considered a special case of delegation. Sim-

ilarlty to the delegation case, mobile code and related data are homomorphically but in this case their are not just sent to a single server, but are passed from one computing node to another. This scenario canbe useful for data collection, where the customer is interested in computing some result which depends on data coming from different sources. Each source (node) executes the encrypted code adding their own input data, computing a new intermediate result without revealing their input. Only the final recipient (the customer) will be able to decrypt the final result.

Multi-Party Computation Multi-Party (MP) computation protocols allow two parties or more parties to compute a public function over secret input data in a way that prevent any party to know the secret input share hold by any other party. This can be achieved with our system as sketched in the Mobile Code use case. In the MP scenario all participants act as both information provider and information recipient. An advantage of our system over the approach of the garbled circuits [2] is that the garbled circuits require much more communication between the interacting parties to generate and exchange the function representation.

**E-Voting** Electronic Voting is one of the earliest and most widely studied application field to have used homomorphic (mostly partially homomorphic, such as ElGamal) encryption to achieve vote privacy. In an election scenario, the homomorphic encryption may act as a powerful tool that enable an untrusted third party provider to compute the tally given the encrypted votes without knowing the content of such votes. One of the first work is that of Benaloh and Tuinstra [20], who used partial homomorphic encryption to implement verifiable secret ballet elections where anyone can verify the tally result. A voter employs such encryption scheme to encrypt his/her vote and as soon as the Polling Station has collected all votes, they are homomorphically tallied without disclosing any single vote and the secret key is used only at the end to decrypt and recover the result for each candidate. One main drawback is that a zero knowledge proof has to be supplied as a proof of validity. H. Jonker et al. [21] underline how fully homomorphic encryption schemes could be a significant improvement in e-voting systems, both supporting addition and multiplication and also preserving the structure of plaintexts.

Zero-knowledge proof Zero-knowledge proof is an important primitive of security protocols which enable one party to prove to another party that a certain statement is true without disclosing any additional information, that is, if the first party needs private information for such proof, it is not disclosed to anybody. It was first introduced by Goldwasser, Micali and Rackoff in 1985 [22]. Since then, it has received noticeble attention from the scientic world, given its potential for authentication system. In such a scenario, a user wants to prove his/her identity to a host by using some secret information (password) without communicating anything of such secret to the server. In this particular case, we have a zero-knowledge proof of knowledge.

Gentry himself shows [17] in his dissertation that homomorphic encryption can be used in the construction of non-interactive zero knowledge (NIZK) proofs of small size.

### 1.2 Background

### 1.2.1 Mathematical background

In order to explain the working of a public key homomorphic cryptosystem, we'll firstly introduce a simple symmetric key scheme.

As encryption key, we choose an odd integer p, such that  $p \in [2^{\eta-1}, 2^{\eta})$  Each plaintext m is made up of a single bit,  $m \in \{0, 1\}$ , and is encrypted as  $c = pq + 2r + m \Rightarrow c \equiv (2r + m) \mod p$ , where r (noise) and q are randomly chosen in suitable intervals, with |2r| < p/2. A ciphertext c is descripted as  $m = (c \mod p) \mod 2$ .

At this point, we can ask ourselves if this scheme is homomorphic with respect to some arithmetic operations. Let's consider then two ciphertexts,  $c_1, c_2$ , such that  $c_1 = pq_1 + 2r_1 + m_1, c_2 = pq_2 + 2r_2 + m_2$ . we have that:

- Addition:  $c_1 + c_2 = p(q_1 + q_2) + 2(r_1 + r_2) + (m_1 + m_2)$

- Multiplication:  $c_1c_2 = p(q_1q_2 + 2q_1r_2 + q_1m_2 + 2r_1q_2 + m_1q_2) + (4r_1r_2 + 2r_1m_2 + 2m_1r_2) + m_1m_2$

The previous scheme, which is a symmetric, can be easily turned in a public key one (still, as a toy scheme with no security guarantee): firstly, we compute a sequence of integers  $x_i = q_i p + 2r_i$ , with  $q_i$ ,  $r_i$  chosen as

previously stated. Such sequence will be the public key, while the integer p will be the secret key. Each  $x_i$  can be viewed as an *encryption of zero*, using the previous scheme. The new asymmetric encryption operation will be:

•

$$c = \sum x_i + m = \sum (q_i p + 2r_i) + m = p \underbrace{\sum_q q_i}_{q} + 2 \underbrace{\sum_r r_i}_{r} + m$$

, where

the summations are intended over a subset of the public key.

Decryption works as before.

6

As we have shown, we can carry out arithmetic operations on ciphertexts and getting them applied to the corresponding plaintexts. Decryption of a cipher text is correct as long as the noise is smaller than p/2. Anyway noise grows when we perform additions and multiplication; more specifically, addition will roughly double the noise while multiplication will square it, so the multiplication is usually the main concern. There are then only a limited number of operations we can perform before the noise becomes too big and the decryption will yield an incorrect result. Such an homomorphic scheme is called a *somewhat* homomorphic encryption scheme.

Before further analyzing the properties of FHE, we want the summarize the main existent groups of homomorphic schemes.

- Schemes preceding the Gentry's were essentially only partial or somewhat homomorphic, supporting limited kind of operations and, above all, only a limited number of such operations. A significant example is Paillier's cryptosystem [23], which supports both addition and multiplication by a constant. Table 1.1 presents a non exhaustive list of homomorphic schemes preceding Gentry's.

- Gentry's original work [17] presents an homomorphic schemes based on the properties of ideal lattices and, most importantly, he introduced the concept of *bootstrappability*, by which a somewhat homomorphic scheme obeying certain properties can be turned in a fully homomorphic one.

- FHE schemes subsequent to Gentry's work fall into three main categories:

- Schemes derived directly from Gentry's ones. Main contributions to optimization have come from Smart and Vercauteren.

| Cryptosystem           | Kind of homo-<br>morphism | Assumption               |

|------------------------|---------------------------|--------------------------|

| RSA [24]               | Multiplicative            | Integer factorization    |

| ElGamal [25]           | Multiplicative            | Computational/Decisional |

|                        |                           | Diffie-Hellman           |

| Pallier [23]           | Additive and              | Computationl/Decisional  |

|                        | scalar multiplica-        | Composite Residuosity    |

|                        | tive                      | Class                    |

| Goldwasser-Micali [26] | Single-bit additive (XOR) | Quadratic Residuosity    |

Table 1.1: Partial homomorphic schemes precedent to Gentry's work

The most secure parameter setting yields a public key size of 2.3 GB.

- Dijk, Gentry, Halevi and Vaikuntanathan's scheme (DGHV) [18] over the integers. It is maybe the most understandable and will be the base for our following discussion. It has been subject to various optimizations and a secure parameter setting gives a public key size of about 802 MB.

- Brakerski and Vaikuntanathan's scheme [19] based on Learning with Errors and Ring Learning with Errors.

For simplicity's sake, in the following we'll focus on the FHE over the integer. Nonetheless, our accelerator can find application also in other FHE schemes, since it is not tied to a specific scheme but rather on the optimization of their common and most expensive arithmetic operations. We will also consider only single bit plaintexts and expressions containing only additions and multiplications mod 2. This is a common assumption in most FHE schemes, where operations over plaintexts reduce to logical XOR and AND. For this reason, functions over plaintexts are often referred to as *circuits*, since they can be expressed as a net of logical gates. An homomorphic encryption function maps a single bit plaintext to a very long integer in the ciphertext codomain. The logical XOR operation therefore will map to integer addition and, likewise, logical AND will map to integer multiplication. A boolean cirtuit will correspond to a polynomial function (additions and multiplications) in

the ciphertext codomain.

Ageneral fully homomorphic encryption scheme comprises four primitives: KeyGen, Encrypt, Decrypt and Evaluate. It is therefore similar to a classic public key cryptosystem, with the addition of the Evaluate function. The Evaluate primitive takes as input a public key pk, a tuple of ciphertexts c, a circuit C (i.e. a boolean expression) and outputs a ciphertext  $c_o$ , obtained applying the circuit on the input c. Additionally, Evaluate must take measures in order to contrast the noise growth, if we want to compute arbitrary circuits.

An encryption scheme  $\xi = (KeyGen, Encrypt, Decrypt, Evaluate)$  is correct for a class S of circuits if it is correct for all circuits  $C \in S$ . It is fully homomorphic if it is correct for any arbitrary circuit.

An additional consideration is that operations on ciphertexts not only increase the noise but also the ciphertext size itself. Therefore, another challenging property we desire is *compactness*, which informally means that the size of the ciphertext output of *Evaluate* does not depend on the size of the computed circuit. An encryption scheme  $\xi = (KeyGen, Encrypt, Decrypt, Evaluate)$  is *compact* if there exists a fixed polynomial bound  $b(\lambda)$ , such that, for any key pair (sk, pk), any circuit C and any finite ciphertext tuple c encrypted with pk, the size of the output of Evaluate(pk, C, c) is no more than  $b(\lambda)$ .

The simple toy scheme we built previously can obviously manage a limited number of operations; such a scheme is therefore a somewhat homomorphic encryption scheme. Gentry proved that we can build a full homomorphic scheme from a somewhat one that can evaluate a little more than is decryption function; such property is the so called bootstrappability. In the following we'll consider an encryption scheme where the decryption function complexity depends only on the security parameter  $\lambda$ . To such scheme we add two augmented decription circuits, both taking a secret key and two ciphertexts, which are firstly decrypted and then added mod 2 in the first circuit or multiplied in the second. The set of these two circuits is denoted by  $D_{\xi}(\lambda)$ .

Let's consider a ciphertext c as the encryption of m under the public key  $pk_1$  with secret key  $sk_1$ . Let  $(pk_2, sk_2)$  be a second key pair. Let  $\overline{sk_1}$  be the encryption of  $sk_1$  under the second public key (given the previous assumption, each bit of  $sk_1$  is encrypted separately) and let  $\bar{c}_i = Encrypt(pk_2, c_i)$  the encryption under  $pk_2$  of each bit of the ciphertext  $\bar{c}$ . Then  $c'' = Evaluate(pk_2, D_{\mathcal{E}}, \langle \overline{sk_1}, \bar{c_1}, \dots, \bar{c_{\gamma}} \rangle)$  yields the plaintext

m encrypted under the new public key  $pk_2$ . This could seem a bit obscure but it is a simple consequence of the homomorphic nature of the scheme: we are considering the decryption function as a boolean circuit whose input bits are those of input bit are those of  $sk_1$  and c. Instead of calculating directly this function, which whould yield the original plaintext m, we evaluate it homomorphically through Evaluate, that is, we consider the polynomial function corresponding to the decrypt boolean function (as stated before), and instead of the original bits of  $sk_1$  and c, we consider their encryption under  $pk_2$ . The evaluation of such fuction, according to the homomorphic property, is an integer which is the encryption under  $pk_2$  of the bit which we would get from evaluating the original boolean function. Such result would be the plaintext bit m, but it is actually encrypted  $pk_2$ . In practice, we removed the original encryption under  $pk_1$  while keeping the encryption under  $pk_2$  (as if we would remove a parcel internal envelope while it is still inside another external envelope). The procedure is shown in Figures 1.1 (a) and (b).

The overall result is to have reencrypted the original plaintext under a new key; the current noise is removed and the reencrypted ciphertext will have just the basic noise of a fresh encryption. This operation could therefore be considered a kind of *refresh*.

It is evident that since the decryption function is evalued as any other function, it contributes to increase the noise contained in the ciphertext. So the somewhat homomorphic encryption scheme, in order to be bootstrappable, must be able to support function at least as much complex as their decryption circuit. Actully, it should support at least one operation in addition to the decryption circuit, in order to have some elbow room for useful computation, before having to refresh the ciphertext. This additional operation must necessary be the multiplication (AND) since it produces the worst noise growth.

More formally, if  $\xi = (KeyGen, Encrypt, Decrypt, Evaluate)$  is an encryption scheme and  $S_{\xi}(\lambda)$  is the set of all the circuits which are correct wrt  $\xi$  for each value of the security parameter  $\lambda$ , then we say that  $\xi$  is bootstrappable if  $D_{\xi}(\lambda) \subseteq S_{\xi}(\lambda)$ . With  $D_{\xi}$  we indicate the augmented decryption circuit, that is, a decryption plus an addition or a multiplication.

A somewhat homomorphic encryption scheme In this paragraph we start to introduce the FHE scheme over the integer of Dijk et al. [18]

10 FHE Accelerator

Figure 1.1: Homomorphic evaluation of decryption function. In (a) is presented the original boolean function, while in (b) the corresponding arithmetic function evalued on the ciphertexts.

by first defining its underline somewhat homorphism. Firstly, we define the parameters of our scheme

- $\gamma$ : bit-length of the integers  $x_i$  in the public key.

- $\eta$ : bit-length of the secret key p.

- $\rho$ : bit-length of the noise  $r_i$ .

- $\tau$ : cardinality of the public key (number of  $x_i$  elements).

Such parameters are subjected to the following constraints

- $\rho = \omega(\log \lambda)$ : protection against brute-force attacks on the noise.

- $\eta \geq \rho\Theta(\lambda log^2\lambda)$ ): in order to support deep enough circuits to evaluate the "squashed decryption circuit".

- $\gamma = \omega(\eta^2 log \lambda)$ : protection against various lattice-based attacks.

- $\tau \geq \gamma + \omega(\log \lambda)$ : to use the leftover hash lemma in the reduction to approximate gcd.

An additional noise parameter is usually introduced:  $\rho' = \rho + \omega(\log \lambda)$ . A possible choice for parameters is  $\rho = \lambda$ ,  $\rho' = 2\lambda$ ,  $\eta = O(\lambda^2)$ ,  $\gamma = O(\lambda^5)$  and  $\tau = \gamma + \lambda$ . An implementation setting is  $\gamma \simeq 2 \cdot 10^7$ ,  $\eta = 2652$ ,  $\rho = 39$  with a public key size of about 802 MB.

We introduce now the somewhat homomorphic encryption scheme after defining the set  $\mathcal{D}_{\gamma,\rho}(p) = \{x = pq + r | q \in \mathbb{Z} \cap [0, 2^{\gamma}/p), r \in \mathbb{Z} \cap (-2^{\rho}, 2^{\rho})\}$

- $KeyGen(\lambda)$ : The secret key p is a  $\eta$ -bit odd integer chosen randomly from  $(2\mathbb{Z}+1)\cap[2^{\eta-1},2^{\eta})$ . For the public key, we choose randomly  $\tau$  elements from the set  $\mathcal{D}_{\gamma,\rho}(p)$  and relabel them so that  $x_0$  is the largest. Repeat until  $x_0$  is odd and  $x_0$  is even mod p.

- Encrypt(pk, m): We chose a random subset  $S \subseteq \{1, 2, ..., \tau\}$  and a random integer  $r \in (-2^{\rho'}, 2^{\rho'})$ . We output  $c = [m + 2r + 2\sum_{i \in S} x_i]_{x_0}$ .

- Evaluate(pk, C, c): apply the circuit function of C to c as operations over the integers and return the result.

12

• Decrypt(sk, c):  $m = (c \mod p) \mod 2 = c - p \cdot \lfloor c/p \rfloor \mod 2 \xrightarrow{p \text{ is odd}} m = (c \mod 2) \oplus (\lfloor c/p \rfloor \mod 2).$

The encryption function is very similar to that of our toy scheme with the main variation that now we calculate also the remainder over  $x_0$ , which is easily explained. Let's consider

$$c = [m + 2r + 2\sum_{i \in S} x_i]_{x_0} \Rightarrow c = m + 2r + 2\sum_{i \in S} x_i + kx_0,$$

$$k \in \mathbb{Z} \Rightarrow c = m + 2r + 2\sum_{i \in S} (pq_i + r_i) + k(pq_0 + r_0) \Rightarrow$$

$$\Rightarrow c = \underbrace{m + 2(r + \sum_{i \in S} r_i)}_{plaintext + noise} + \underbrace{p(\sum_{i \in S} 2q_i)}_{multiple \ of \ p} + \underbrace{k(pq_0 + r_0)}_{\equiv 2 \ \text{mod} \ p}$$

If k is small  $\Rightarrow k \leq \tau$ . That's why we chose  $x_0$  to be even modulus p, so that it doesn't hide the parity of m.

Following Gentry's blueprint, we define a permitted circuit as one such that  $\forall \alpha \geq 1$  and any set of integers  $\leq 2^{\alpha(\rho'+2)}$  in absolute value, the output is at most  $2^{\alpha(\eta-4)}$ .  $\mathcal{C}_{\mathcal{E}}$  denotes the set of permitted circuits. It can be proven that the previous scheme is correct for  $\mathcal{C}_{\mathcal{E}}$ . We recall that a fresh ciphertext has noise at most  $2^{\rho'-2}$ . if we apply Evaluate to it with a permitted circuit we have an output with noise at most  $2^{\eta-4} < p/8$ . A bound of p/2 would suffice, but this stricter bound will be useful in the following. Before continuing, we underline that the noise growth depends mainly by the multiplicative depth of the circuit, that is the degree of the multivariate polynomial homomorphically computed by the circuit.

At first glance it would seem possible to use the modular reduction by  $x_0$  to keep the ciphertext size bounded during *Evaluate*. Unfortunately, it is not possible since after only one multiplication the ciphertext size gets much larger than  $x_0$  so modular reduction will add a large multiple of  $x_0$  introducing too much noise. Indeed, we have that for a *fresh* ciphertext  $c < x_0$  and in the worst case  $c \approx x_0$ . For simplicity, we consider a squaring operation of c. Modular reduction is accomplished by adding an appropriate multiple of  $x_0$ , that is  $c' = c^2 + kx_0 k \in \mathbb{Z}$ ; k is roughly the quotient of  $c^2$  by  $x_0 \Rightarrow k \approx \frac{c^2}{x_0} \approx \frac{x_0^2}{x_0} = x_0$ , which is much larger than the permitted noise. We observe that for bigger  $x_0$  we

have smaller k. Therefore, we add to the public key more elements like  $x_i' = q_i'p + 2r_i'$  where the  $r_i'$  are choosen as before but the  $q_i'$  are larger. More precisely  $q_i' \in \mathbb{Z} \cap [2^{\gamma+i-1}/p, 2^{\gamma+i}/p), r_i' \in \mathbb{Z} \cap (-2^\rho, 2^\rho)$  with  $i = 0, 1, \ldots, \gamma$  Whenever c get greater than  $2^\gamma$ , we first reduce it modulo  $x_\gamma'$ , then modulo  $x_{\gamma-1}'$  and so on down to  $x_0'$  (decreasing order). Without this variation, the output of *Evaluate* on two circuits that represent the same polynomial will be the same, but with this modification noise could be bigger in one case than in the other, yielding different outputs.

Scheme security The security of the scheme is based on the assumption of the hardness of the approximate integer greatest common divisors (approximate GCD). The  $(\rho, \eta, \gamma)$ -approximate GCD problem is defined as follow: given a polynomial number of samples from  $\mathcal{D}_{\gamma,\rho}(p)$  for a random  $\eta$ -bit odd integer p, find p. Intuitively, the problem consists into finding p given a polynomial number of p-armultiples of p.

A fully homomorphic scheme According to Gentry's approach, a fully homomorphic scheme can be built starting from a *somewhat* homomorphic one which is also *bootstrappable*. In order to be bootstrappable, it should be able to homomorphically evaluate at least a circuit a bit more complex than the its own decryption circuit. It can be proved that the decryption circuit of the previous scheme doesn't belong to the set of permitted circuits. Gentry's approach is to transform the scheme to realize a *squashed* decryption circuit (that is, simpler and, above all, shallower). The is achieved by adding extra information to the public key about the secret key, making decryption phase more efficient. The ciphertext will contain more information in order to help decryption.

We describe then a modified scheme, with a squashed decryption function. We'll use three additional parameters:  $\kappa, \theta, \Theta$ . We add to the public key a set  $\mathbf{y} = \{y_0, \dots, y_{\Theta}\}$  of rational numbers in [0, 2), so that there is a sparse subset S of size  $\theta$  which satisfy  $\sum_{i \in S} y_i \approx \frac{1}{p} \mod 2$ . As secret key, instead of using p we use the indicator vector of S.

The secret key is s and the public key (pk, y).

The modified functions are as follow

- KeyGen:

- Create sk and pk as before. Set  $x_p = round(2^{\kappa}/p)$ . Choose a random  $\Theta$ -bit vector s with Hamming weight  $\theta$  and let

FHE Accelerator

| Instance | λ  | ρ  | $\eta$ | $\gamma \cdot 10^{-6}$ | au   | Θ    | Publi | c key size |

|----------|----|----|--------|------------------------|------|------|-------|------------|

| Toy      | 42 | 27 | 1026   | 0.15                   | 158  | 144  | 77    | KB         |

| Small    | 52 | 41 | 1558   | 0.83                   | 572  | 533  | 437   | KB         |

| Medium   | 62 | 56 | 2128   | 4.20                   | 2110 | 1972 | 2.21  | MB         |

| Large    | 72 | 71 | 2698   | 19.35                  | 7659 | 7897 | 10.3  | MB         |

Table 1.2: Concrete parameters for the optimized FHE schemes

$$S = \{i | s_i = 1\}.$$

14

- Choose  $\Theta$  random integers  $u_i \in \mathbb{Z} \cap [0, 2^{\kappa+1})$  such that  $\sum_{i \in S} u_i = x_p \mod 2$ . Set  $y_i = u_i/2^{\kappa}$ . Each  $y_i$  is so a positive number in ;2 with  $\kappa$  bits after the binary point.

- We get, as previously stated, that  $\sum_{i \in S} y_i = (\frac{1}{p} \Delta_p) \mod 2$  with the error  $\Delta_p < 2^{-\kappa}$ .

- *Encrypt*: proceeds as before but at the end we do the following additional steps:

- Compute  $z_i = c \cdot y_i \mod 2$ , keeping only  $n = \lceil log\theta \rceil + 3$  bits after the point.

- Output both c and  $z = \langle z_1, \ldots, z_{\Theta} \rangle$ .

- Decrypt:  $m' = (c round(\sum_i s_i z_i)) \mod 2$ .

It can be proved that this modified scheme is still correct for the set  $C(\mathcal{P}_{\mathcal{E}})$  of circuits that compute the permitted polynomials, as previously defined. If  $D_{\mathcal{E}}$  is the set of augmented decryption circuits, it can also be prove then  $D_{\mathcal{E}} \subseteq C(\mathcal{P}_{\mathcal{E}})$ ; that is,  $\mathcal{E}$  is bootstrappable. We will omit here such proofs for space reasons.

**Optimizations** There have been several efforts toward optimizing the scheme, in order to reduce time complexity and especially the public key size. Significant optimizations have been proposed by Coron et al. [27][28]. Their most important contributions are public key compression and modulus switching Table 1.2 reports the concrete parameters for the best of such optimized schemes.

### 1.2.2 Previous works

Before describing the approach we followed, in this section we'll firstly reviews the existing research works concerning the implementation of the HE primitives. We are interested here in the so-called Fully Homomorphic Encryption (FHE) [17], allowing arbitrary and unlimited sequences of operations on encrypted data. A first implementation of a variant of the original Gentry's scheme [17] was proposed by Gentry and Halevi [29]. Their implementation, despite various optimizations and small-size security parameters, takes more than one second for encrypting a single bit on an Intel Xeon server. Recent software implementations include [30, 31]. An open-source implementation, hcrypt [32] is available on-line. Another library [33] contains an optimized implementation that reaches a significant speed-up over the previous implementation. Several research works concerning FHE computing platforms have looked for alternative architectures, particularly GPUs and FPGAs. GPUs offer high throughput and efficiency for data intensive computing, such as vector and linear algebra problems. FHE schemes can benefit from this architecture, since they are highly parallelizable with respect to data. FPGA technology offers, on the other hand, the flexibility of implementing a custom and targeted architecture at a low cost, as opposed to Application Specific Integrated Circuits (ASICs). Moreover, several FPGAs include built-in optimized blocks for multiplyand-accumulate operations, which can be effectively exploited when implementing large multiplication. A recent GPU implementation is presented in [34], based on NVIDIA GTX 690. It reaches spead-ups of 174, 7, and 13 for encryption, decryption and reencryption with respect to Gentry and Halevi's software implementation. Other recent implementations on GPUs are [35, 36]. Among the FPGA implementations, one of the most recent is presented in [1], which compares FPGAs and GPUs, namely Altera Stratix V and NVIDIA Tesla C2050. Their implementation efforts are fundamentally focused on the FFT multiplier building block. The authors conclude that the FPGA version is at least twice as fast as the GPU one, with lower power consumption. [37] and [38] proposes a full custom ASIC implementation of large-operand multiplication. The design includes also a 768 Kbit cache to minimize I/O transactions. A single multiplication is performed in 7.7 ms at 666 MHz. The authors also built the first custom hardware implementation [39] of the cryptographic primitives of Gentry-Halevi FHE scheme. The design includes optimizations previously introduced in [34] to reduce the number of FFT computations. Speed-up of 1.24, 99.44, and 10.32 for decryption, encryption and recryption are achieved compared to the software implementation of Gentry and Halevi.

As mentioned, most existing implementations focus around optimizing the most time consuming operations used by the various encryption schemes: multiplication and modular reduction. Such operations are performed on very large operands (millions of bits) and can benefit from better asymptotic algorithms. Most current implementations rely on the Schonhage-Strassen algorithm (SSA) for the multiplication of large integers. The SSA algorithm exploits the properties of the Discrete Fourier Transform over integers, and it pays off for operands of at least 100,000 bits.

Last, [40] proposed an FFT-based large integer multiplier, along with a Barrett reduction module. Their design was implemented on a Xilinx Virtex-7 FPGA and included the encryption primitive of Coron *et al.* FHE scheme [41, 42]. The results show a remarkable speed-up compared to existing software implementations.

Our research follows this work line, trying to realize FPGA based acceleration support for the execution of the most time consuming operations required by FHE schemes. In the following sections we will present our approach adopted and the results obtained so far.

### 1.3 Approach followed

Our research work is aimed to support probabilistic, fully homomorphic algorithms which comprise various approaches, such as the integer-based approach first introduced by M. van Dijk et al., and schemes based on Lattice problems and Learning with Errors. We aim to exploit the potential of a highly-customized FPGA design for accelerating the most time consuming operations used by the encryption primitives: long-integer multiplication and modular reduction. Since the latter can be reduced to a combination of one or more multiplications, the priority is on accelerating multiplication on ultra-large operands (in the order of millions of bits). The FHE primitives can be implemented on the top of our accelerator, i.e. in software, this way decoupling the proposed design from the specific FHE scheme. We explored the efficient implementation of asymptotically faster (but inherently more complex)

multiplication/reduction algorithms in place of usual schemes used for moderately large operands (thousands of bits).

The main algorithms available to perform integer multiplication are the following (in decreasing order of complexity):

- School-book (plain)  $(O(n^2))$

- Karatsuba  $(O(n^{log3}) \approx O(n^{1.585}))$

- Toom-Cook  $(O(n^{\frac{\log 5}{\log 3}}) \approx O(n^{1.465}))$

- Schönhage-Strassen  $(O(n \cdot log n \cdot log log n))$

- Fürer  $(O(n \cdot log(n) \cdot 2^{O(log^*n)})$

Algorithms with lower computational complexity have higher hidden constants, since they are based on a more complex approach. Karatsuba and Toom-Cook algorithms are best suited for middle sized operand (in the order of a thousand bits) such as those required by the RSA scheme.

While Fürer's algorithm is almost prohibitively complex, Schönhage-Strassen algorithm (SSA), which exploits the properties of the Number-Theoretic Discrete Fourier Transform, can offer an asymptotically better complexity for operands of at least 100,000 bits, where the cost of hidden constant is better amortized.

### Algorithm 1. Schönhage-Strassen multiplication

Input: operands x and y, prime modulus p, unit radix  $\omega$ , DFT point number k, word width b.

Output:  $z = x \cdot y$ .

• Decompose operand x into a sequence  $x_t$  of b bit words, with  $0 \le t < k$ . The first half of such sequence  $(x_0 \text{ to } x_{k/2-1})$  is made up with actual bits from operand x, while the second half of the sequence  $(x_{k/2} \text{ to } x_{k-1})$  is filled with zeros. The same operation is performed on operand y. Such sequences are considered as polynomial coefficients and the relationship with the original operands is given by Equation (1.1)

$$x = \sum_{i=0}^{k} (x_i \mod p) \cdot 2^{i \cdot b}, \ y = \sum_{i=0}^{k} (y_i \mod p) \cdot 2^{i \cdot b}$$

(1.1)

18 FHE Accelerator

• Compute a k-point integer DFT over the finite field  $\mathbb{Z}/p\mathbb{Z}$  of sequences  $x_t$  and  $y_t$ , getting the sequences  $X_t$  and  $Y_t$ , with  $0 \le t < k$ . The operations are summarized in Equation (1.2)

$$X_t = \sum_{i=0}^{k-1} x_i \cdot \omega^{i \cdot t} \pmod{p}, \ Y_t = \sum_{i=0}^{k-1} y_i \cdot \omega^{i \cdot t} \pmod{p}$$

(1.2)

• Compute a point-wise multiplication over the finite field  $\mathbb{Z}/p\mathbb{Z}$ , getting a k-point sequence  $Z_t$ , with  $0 \le t < k$ , as per Equation (1.3)

$$Z_t = X_t \times Y_t \pmod{p} \tag{1.3}$$

• Compute the k-point Inverse DFT of sequence  $Z_t$  over the finite field  $\mathbb{Z}/p\mathbb{Z}$ , getting the sequence  $z_t$  of length k, as per Equation (1.4)

$$z_t = k^{-1} \sum_{i=0}^{k-1} Z_i \omega^{-i \cdot t} \pmod{p}$$

(1.4)

• Compute the final result by performing the sum in Equation (1.5), propagating the long carry chain

$$z = \sum_{i=0}^{k} z_i \cdot 2^{i \cdot b} \tag{1.5}$$

The computational complexity of SSA is  $O(n \cdot \log n \cdot \log \log n)$ . The most time consuming operation in SSA is the computation of the DFT (and Inverse DFT) over the integer. The DFT is a well known transform, but it is more commonly found in signal processing, where it is defined on the complex field  $\mathbb C$  and where the Fourier domain has a cllear and intuitively interpretation in terms of frequencies which compose a given signal. Anyway it is possible to define a Generalized DFT, which applies to a more general algebraic structure and is more abstract in concept (the Fourier domain has no interpretation in terms of frequencies), but nonetheless the most relevant DFT properties (especially the theorem of convolution) still hold. The complex exponentials are replaced by more general roots of unity, which anyways have to obey some properties, namely being primitive and principal roots. The Generalized DFT can then be applied to the modular integer arithmetic, subject to some constraints. We begin firstly by proving the following theorem.

**Theorem 1.1** Let R be a commutative unitary ring, N a natural number with  $N \geq 2$  and  $N \cdot 1_R$  a unit in the ring and suppose  $\omega$  is a  $N^{th}$  principal root of unity. Then the homomorphism

$$\psi: R[x] \longrightarrow R^N$$

$f(x) \longmapsto (f(\omega^0), \dots, f(\omega^{N-1}))$

is surjettive with kernel  $(x^N - 1)$ .

The induced isomorphism  $\varphi: R[X]/(x^N-1) \to R^N$  is called the Discrete Fourier Transform with respect to  $\omega$ . It is represented by the matrix  $DFT(N,\omega) = (\omega^{pq})_{1 \le p,q \le N} \in GL(N,R)$  and the inverse transformation by  $IDFT(N,\omega) = N^{-1} \cdot (\omega^{-pq})_{1 \le p,q \le N} = N^{-1}DFT(N,\omega^{-1})$ .

Proof.  $\ker \psi = \{f(x) \in R[x] : \psi(f(x)) = \underline{0} \Rightarrow (f(\omega^0), f(\omega^1), \dots, f(\omega^{N-1})) = (0, 0, \dots, 0)$ Therefore  $\ker \psi = \cap_{i=0}^{N-1} (x - \omega^i)$ . We must show that  $\ker \psi = (x^N - 1)$ .

Therefore  $\ker \psi = \bigcap_{i=0}^{N-1} (x-\omega^i)$ . We must show that  $\ker \psi = (x^N-1)$ . By induction on j we get then that for  $j=0, f(\omega^j)=0 \Rightarrow f(1)=0 \Rightarrow f(x)=(x-1)\cdot g(x)$ .

Now let's suppose that  $\forall i: 0 \leq i \leq j, N > j > 0$  we have that  $f(\omega^i) = \prod_{i=0}^j (x - \omega^i) \cdot g(x)$ .

Now let's consider the next component:  $f(\omega^{j+1}) = 0 \Rightarrow \prod_{i=0}^{j} (\omega^{j+1} - \omega^i) \cdot g(\omega^{j+1}) = 0$

We can write also  $\prod_{i=0}^{j} \omega^{i}(\omega^{j+1-i}-1) \cdot g(\omega^{j+1}) = 0$ . By the principality of  $\omega$ , the factors  $(\omega^{j+1-i}-1)$  are not zero divisors  $\Rightarrow g(\omega^{j+1}) = 0 \Rightarrow g(x) = (x-\omega^{j+1}) \cdot u(x)^{2}$

Then ker  $\psi = (x^N - 1)$ . The induced homomorphism  $\varphi : R[X]/(x^N - 1) \to im(\psi)$  is indeed an isomorphism with associated matrix  $DFT(N,\omega)$ .

We still need to show that  $\varphi$  is surjective, which can be done showing that  $DFT(N,\omega)$  is invertible, that is  $DFT(N,\omega) \cdot IDFT(N,\omega) = I(N)$ .

$$a_{p,r} = \sum_{q=0}^{N-1} \omega^{pq} \cdot N^{-1} \omega^{-qr} = N^{-1} \cdot \sum_{q=0}^{N-1} \omega^{pq} \cdot \omega^{-qr} =$$

$<sup>^1</sup>$  Unit means an invertible element. Not to be confused with unity. If N is invertible then it cannot be divisible by the characteristic. So we are implicitly impling that  $\omega$  is also primitive.

$<sup>{}^2\</sup>cap_{i=0}^{N-1}(x-\omega^i)$  Intersection of the ideals generated by  $(x-\omega^i)$ ,, i.e. the set of the polynomials  $(x-\omega^i)\cdot g(x)$

$$N^{-1} \cdot \sum_{q=0}^{N-1} \omega^{q(p-r)} = \begin{cases} N^{-1} \sum_{q=0}^{N-1} 1 = 1 & for \, p = r \\ 0 & for \, p \neq r \end{cases}$$

The last descends from the principality of  $\omega$ .

In order to apply the DFT to a modular integer ring  $\mathbb{Z}_M$ , some properties must be satisfied: firstly, the number of points N must be an invertible element in  $\mathbb{Z}_M$ , which is satisfied if  $\gcd(N,M)=1$ . Then we must find a primitive root of unity, that is, a root of unity with order N. The multiplicative group generated by such root is cyclic and, according to Lagrange's theorem, its order must be a divisor of the order of any of its super-groups. The maximal multiplicative group in  $\mathbb{Z}_M$  is given by all its invertible elements. It is denoted  $\mathbb{Z}_M^*$  and its order if  $\varphi(M)$ , where  $\varphi$  is the *totient* function. Therefore we must have that N divides  $\varphi(M)$ .

Computing directly the DFT would give a time complexity of  $O(N^2)$ ; a more efficient method if using the Fast Fourier Transform algorithm of Cooley-Tukey [43] with a complexity of  $O(N \cdot log N)$ . It can be showed that their divide-et-impera method (which was actually invented by C.F. Gauss) can be applied also in the case of the DFT over the integer. Instead of using the classic Radix-2 based implementation, we choose to apply the generalized FFT approach in order to decompose the overall FFT into higher order sub-FFTs.

Starting from the basic DFT formula  $F[k] = \sum_{n=0}^{N-1} f[n] \omega_N^{kn}$ , we decompose N as  $N = N_1 \cdot N_2$ , so the input and output vectors can be split into  $N_1$  sub-sequences of length  $N_2$ . Let  $n = N_2 n_1 + n_2$  and  $k = N_1 k_2 + k_1$  with  $n_1, k_1 \in \{0, 1, \dots, N_1 - 1\}$  and  $n_2, k_2 \in \{0, 1, \dots, N_2 - 1\}$ . Then the DFT can be written as:

$$F[N_1k_2 + k_1] = \sum_{n=0}^{N-1} f[n]\omega_N^{kn} =$$

$$= \sum_{n_2=0}^{N_2-1} \left[ \left( \sum_{n_1=0}^{N_1-1} f[N_2n_1 + n_2] \cdot \omega_{N_1}^{n_1k_1} \right) \cdot \omega_N^{n_2k_1} \right] \cdot \omega_{N_2}^{n_2k_2}$$

(1.6)

Despite the better time complexity, one of the main problem of the FFT (regardless of the chosen radix) is that its memory access pattern is

Figure 1.2: Butterfly scheme of the Radix-2 FFT.

highly non sequential, therefore badly affecting access time for cache and DDR memory. As can be seen from Figure 1.2 for the case of Radix-2 FFT, memory accesses are more spread out as we proceed from our stage to the next one. This is the so called *butterly* access pattern. In custom hardware implementation, it is usual to use a scratchpad memory, with a dedicated address space and outside of any cache hierarchy. We'll follow a similar approach and we'll add a dedicated logic to manage the particular FFT access pattern.

We choose to perform the computation in the finite field  $\mathbb{Z}/p\mathbb{Z}$ , with prime p. By selecting a proper prime p, the modular multiplication in the finite field can be computed rapidly as simple shifts. In our implementation, we choose the Solinas prime number  $p=2^{64}-2^{32}+1$ , since its particular properties greatly simplify arithmetic computing, especially multiplication. Table 1.3 shows some possible choices for the FFT modulus from the scientific literature, along with the corresponding bit width requirement, a feasible choice for the FFT number of points k and the relative root of unity  $\omega$ .

In the following, we suppose to deal with operands of 786432 bits, which corresponds to the small security parameter setting for DGHV

22 FHE Accelerator

|                   | Modulus               | Bit width | k   | $\omega$ |

|-------------------|-----------------------|-----------|-----|----------|

| Special form [44] | $2^{32} + 1$          | 33        | 64  | 2        |

| Special form [44] | $2^{64} + 1$          | 65        | 128 | 2        |

| Solinas form [45] | $2^{64} - 2^{32} + 1$ | 64        | 128 | 7        |

| General form [46] | $2^{32} - 2^{20} + 1$ | 32        | 64  | 17       |

Table 1.3: Possible choices of modulus and corresponding parameters

and is used in many research papers. Operands are decomposed into 32K coefficients of 24 bits.

We need to apply FFT on 64K points, in order to accommodate the multiplication result. By applying Equation 1.6 recursively on the 64K-point DFT, it can be computed with three stages using radix-64 and radix-16 sub-transforms:

$$\begin{split} &\sum_{n_1=0}^{N_1-1}\sum_{n_2=0}^{N_2-1}\left[\sum_{n_3=0}^{N_3-1}\left(a[n]\omega_{N_3}^{n_3k_3}\right)\omega_{N_2N_3}^{n_2k_3}\omega_{N_2}^{n_2k_2}\right]\omega_N^{n_1k_2'}\omega_{N_1}^{n_1k_1}=\\ &=\sum_{n_1=0}^{15}\sum_{n_2=0}^{63}\left[\sum_{n_3=0}^{63}\left(a[n]\omega_{N_3}^{n_3k_3}\right)\omega_{N_2N_3}^{n_2k_3}\omega_{N_2}^{n_2k_2}\right]\omega_N^{n_1k_2'}\omega_{N_1}^{n_1k_1} \end{split} \tag{1.7}$$

where

$$n = N_1 N_2 n_3 + N_1 n_2 + n_1,$$

$$k_2' = k_3 + N_3 k_2$$

Each stage can be efficiently parallelized, according to the available computing resources.

### 1.4 Architecture of the FPGA-based accelerator

The essential challenge addressed by this work is the support for ultralarge-operand FFT computation. One design objective we set for the proposed accelerator was the inherent support for scalability to ultralarge operands which, unlike many cryptographic primitives in different contests, may require a flexible and composable design solution applicable either to on- or off-chip scenarios, possibly in multi-FPGA settings available on the server side. Consequently, for the implementation of

the 64K-point FFT building block, we devised a flexible distributed approach, relying on several nodes connected in a hypercube topology, which matches exactly the logical topology of the distributed FFT algorithm. The solution was initially prototyped on a multi-board platform based on low-end devices (Altera Cyclone V) then extended to a hybrid on-/off-chip solution relying on a larger device, i.e. an Altera Stratix V FPGA. The distributed approach, distinguishing our proposal from previous related works like [1], matches very well the FFT computation and ensures several advantages compared to shared memory approaches, such as better scalability and reduced use of global routing resources, which may be a major performance bottleneck especially on FPGAs. Using a hypercube topology, the number of communication stages for FFT computation is the hypercube dimension d. Figure 1.5 shows the hypercube network in the case of four computing nodes; Figure 1.6 shows instead the case for eight computing nodes.

In each stage, a node communicates only with one of its d neighbors, one for each stage.

The number of computation stages l instead depends on the FFT decomposition, as previously shown. We must have l > d in order to

Figure 1.3: Architecture of a 64K FFT processing element.

Figure 1.4: Data distribution.

correctly interleave computation and communication. If l>d+1, communication takes places only after the first d computation stages while the subsequent stages are computation only. The overall architecture of a single node, which we will call  $Processing\ Element$ , is shown in Figure 1.3.

Figure 1.5: Hypercube topology for a system comprising four Processing Elements.

Figure 1.6: Hypercube topology for a system comprising eight Processing Elements.

The core computing element is the Radix-64/16 FFT unit, which computes the basic sub-transforms. Since in our distributed scheme communication will indeed overlap with computing, double buffering is used: while a buffer is feeding current input values, the other one is filled with new values coming partly by the same node and partly from one of its neighbors. At the end of a computation stage, the roles of the buffers are swapped. Buffers are based on a banked architecture which uses the SRAM primitive blocks of the underlying FPGA architecture. Additionally, we also need a group of modular multipliers for twiddle factor multiplications, required between two consecutive FFT computation stages. The data route component is responsible for the proper ordering of FFT output points before writing in the memory buffers.

#### 1.4.1 Data distribution and exchange pattern

Below we consider the computing of a 64K-point FFT with four processing elements. In the initial data distribution phase, the 64K elements vector is partitioned among the four processing elements, considering also the proper decomposition reordering. Then, computing and data exchange stages take place, in a interleaved (but actually overlapped) way. During a computing stage each node can execute in a completely independent way.

We recall also that, according to the previous formula, we can de-

26 FHE Accelerator

compose the 64K FFT as per Equation 1.7. Figure 1.4 summarizes the sequence of computing and communication stages: bold style is used to highlight the index (among  $n_1$ ,  $n_2$ , and  $n_3$ ) involved in the current sub-FFT computing and subsequent data exchange.

Figure 1.7: Architecture of the baseline Radix-64 unit [1].

#### 1.4.2 FFT-64 unit

The Radix-64 unit (or FFT-64) is the basic building block which is capable of computing the sub-transforms that make up the overall FFT. It can be easily extended for computing also Radix-16 FFT, though this will not be shown here. In the chosen finite field, the 64<sup>th</sup> root of unity is 8, so multiplications in the FFT formula become just shifts, as follows:

$$A[k] = \sum_{i=0}^{63} a[i]\omega_{64}^{i \cdot k} = \sum_{i=0}^{63} a[i]8^{i \cdot k} \pmod{p}$$

(1.8)

Since  $8^{64} \pmod{p} = 2^{192} \pmod{p} = 1$ , no intermediate value can exceed 192 bits.

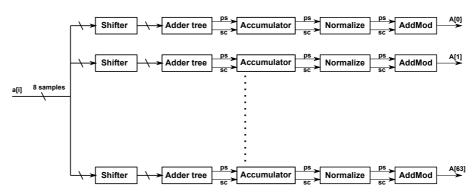

The unit proposed here builds on a baseline scheme [1] shown in Figure 1.7. Input samples are read 8-by-8 and are fed to 64 separated computing chains, one for each frequency component. Each chain comprises a shifter bank, where the eight samples are multiplied by their respective twiddle factor. Shifted values are summed by an adder tree to produce a partial sum. To avoid the latency of long carry chains, a carry save solution is adopted. The output is then made up of two vectors, which are not merged until the very last block (AddMod). The

accumulator will sum up the partial sums in eight consecutive clock cycles. After the eight clock cycles, the transform is complete and the value in the accumulator is modular reduced. The *Normalize* block computes a first coarse reduction by applying Equation 1.9, which applies to 128-bit numbers and exploits the properties of the chosen modulus:

$$a \cdot 2^{96} + b \cdot 2^{64} + c \cdot 2^{32} + d = 2^{32}(b+c) - a - b + d$$

(1.9)

The result will require at most one extra addition or subtraction with the module p. This last operation is performed in the AddMod component.

The baseline scheme is highly redundant since much work can be shared among the components. Our architecture exploits such redundancy through several structural solutions, which, as will be shown in the implementation details, result in a significant reduction of area usage and higher parallelism.

In order to exploit common work between the FFT components, we apply Equation 1.6 to the 64-point FFT:

$$\sum_{i=0}^{63} a_i \omega^{i \cdot k} = \sum_{j=0}^{7} \left[ \left( \sum_{i=0}^{7} a_{i \cdot 8+j} \omega_8^{i \cdot k_1} \right) \cdot \omega_{64}^{j \cdot k_1} \right] \cdot \omega_8^{j \cdot k_2} =$$

$$= \sum_{j=0}^{7} \left( \sum_{i=0}^{7} a_{i \cdot 8+j} \omega_8^{i \cdot k_1} \cdot \omega_{64}^{j \cdot k_1} \right) \cdot \omega_8^{j \cdot k_2}$$

(1.10)

The expression between parenthesis is computed by the first stage in Figure 1.8, where eight samples from the memory are shifted and summed; This is done only for eight frequency components (denoted by  $k_1$ ). Then, such partial sums are multiplied by the twiddle factor  $\omega_8^{j \cdot k_2}$  while the external sum is performed by each accumulator. The multiplication by  $\omega_8^{j \cdot k_2}$  leads to eight possible shifts, but they can be reduced to four if we consider that one half of the twiddle factors are the opposite of the other half (the partial sum will be subtracted in the accumulator instead of being summed). The four factors needed are then  $2^0$ ,  $2^{24}$ ,  $2^{48}$ , and  $2^{72}$  (respectively, no shift, shift by 24, 48, and 72 bits). Accumulators can be thought of as being partitioned into eight blocks of eight accumulators (block number corresponds to  $k_2$  in Equation 1.10). Each block contains a multiplexer selecting which of the four shifts is needed, according to the block number and the current computing step

Figure 1.8: Architecture of FFT64 unit.

(respectively, index  $k_2$  and j). Each block receives also a *subtract* signal (not shown in figure).

The first stage is itself optimized by computing only four of the eight components using the relation:

$$\sum_{i=0}^{7} a_{i\cdot 8+j} \omega_8^{i\cdot k_1} \cdot \omega_{64}^{j\cdot k_1} = \sum_{i=0}^{7} a_{i\cdot 8+j} \omega_8^{i\cdot (k_1'+4)} \cdot \omega_{64}^{j\cdot (k_1'+4)} =$$

$$= \sum_{i=0}^{7} a_{i \cdot 8+j} \omega_8^{i \cdot k_1'} \cdot \omega_2^i \cdot \omega_{64}^{j \cdot k_1'} \cdot \omega_{16}^j \text{ for } k = 4, 5, 6, 7$$

We can see that components 4 to 7 can be computed similarly to the first four, except for the multiplication by a factor  $\omega_{16}^{j}$  and the fact the in the summation odd terms are taken with negative sign. This is done by modifying the adder tree so that it outputs also the difference between the sums of even and odd terms (such modification adds very little complexity to the adder tree).

After eight computing steps, the accumulators contain the FFT output which needs to be modular reduced. While the baseline scheme uses 64 modular reduction components, one for each accumulator, we observe that the maximum average throughput, even in a fully pipelined solution, is eight components per clock cycle. Consequently, we use only

eight modular reductors, one for each accumulator block, preceded by a multiplexer which switches to a different component at each clock cycle. So we yield exactly eight frequency components for each clock cycle. Our solution has a twofold advantage: First, it reduces the area occupancy of the FFT64 unit and the memory parallelism required (eight words vs. 64). Second, it realizes part of the work of the Data Route component, since at every clock cycle we produce eight values which are appropriately spaced out for memory writing.

We also identified a couple of minor optimizations. We merged carry-save vectors immediately after the adder tree, reducing area usage. The carry propagation latency penalty can be mitigated by adding a pipeline stage. Furthermore, before Stage 1, we reduce the bit-width of each value by applying Equation 1.9. This further reduces the area, particularly routing resource usage.

Last, we recall that the FFT-64 unit can be adapted, with minor modifications, to compute also Radix-8, Radix-16, and Radix-32 FFTs. This gives us greater flexibility in choosing an FFT order other than 64K.

#### 1.4.3 Internal Bank Memory

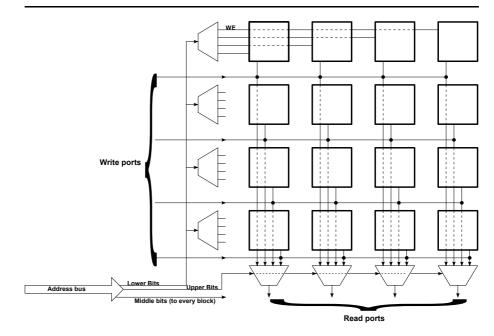

Our internal memory needs to support the specific FFT memory access pattern yet guarantee an appropriate degree of parallelism. A simple *linear* bank memory ensures parallel read accesses (with consecutive words in a row mapped to different banks) but it would cause write accesses to collide on the same bank. These considerations led us to adopt a two-dimensional bank scheme as in Figure 1.9. Each square is a basic memory block, which is dual port SRAM, with a depth of 256 words and word-width of 64 bits implemented as native FPGA memory blocks (namely, two Altera M20K hard core blocks).

A 4x4 array of basic memory blocks gives a size of 256Kb which can hold a vector of 4096 points. The scheme in the figure considers only one of the dual port of a basic block, for visual clarity. Read access is column-wise, write access row-wise. Access parallelism is eight words per clock cycle, either during reading or writing.

30 FHE Accelerator

Figure 1.9: Architecture of banked memory buffer.

### 1.4.4 Modular multiplier

The output points of inner FFTs have to be multiplied by appropriate twiddle factors before they can be used by the external FFT. We chose to use DSP blocks for greater efficiency in terms of area and speed. To realize 64x64 multiplication we can split our operands in 32-bit components and use a basic 32x32-bit DSP multiplier, which requires only two DSP blocks. Using school-book multiplication, four 32x32-bit multipliers are needed; partial products are then summed and modular reduced using Equation 1.9.

#### 1.4.5 Data route

The job of this component is to properly order the output points coming from the modular multipliers, ensuring their correct writing in memory as well as computing the correct addresses according to the current computation step. As mentioned earlier, the complexity of this component is greatly reduced since part of its job is performed by the FFT-64 unit. In fact, it is just a memory address generator.

## 1.5 Implementation and performance

To implement the proposed accelerator, we targeted a Stratix V 5SGSMD8N3F45I4 FPGA, as in [1], using VHDL as the design entry language. Most of the implementation effort was put on the Radix-64 unit, the banked memory, and modular multipliers. All of them have been adequately tested and work as expected. By careful pipelining some subsystems, the components could be synthesized with an operating frequency of 200 MHz.

Below we present a performance estimate, first addressing the FFT and then the SSA multiplication. The FFT-64 unit is able to output an FFT every eight clock cycles, while a FFT-16 will take two clock cycles. A single 64K points FFT will take:

$$T_{FFT} = 2 \cdot (T_C \cdot 8 \cdot 1024)/P + (T_C \cdot 2) \cdot 4096/P$$

where  $T_C$  is the clock period, i.e. 5 ns, while P is the number of Processing Elements (here, four). The first term refers to the first two stages, with 1024 FFTs on 64 points. The second term refers to the last stage where 4096 FFTs on 16 points are computed.

By replacing the clock period and using four Processing Elements, we get

$$T_{FFT} = 20480ns + 10240ns \approx 30.7 \mu s$$

A full SSA multiplication requires three FFTs (two direct FFTs for the inputs and one inverse FFT for the output). Besides we must perform a component-wise multiplication on two vector of 64K components and the final carry recovery addition on the inverse FFT components. The remaining resources can accommodate at least 32 additional modular multipliers for component-wise multiplication, yielding:

$$T_{DOTPROD} = T_C \cdot 65536/32 \approx 10.2 \mu s$$

The final carry recovery can be efficiently computed with an *ad hoc* adder structure, which is th object of another research work. Its maximum delay is approximately  $20\mu s$ . So the overall time for a complete SSA multiplication is  $\approx 122\mu s$ .