# TESI DI DOTTORATO

### Università degli Studi di Napoli "Federico II"

### DIPARTIMENTO DI INGEGNERIA ELETTRONICA E DELLE TELECOMUNICAZIONI

DOTTORATO DI RICERCA IN Ingegneria Elettronica e delle Telecomunicazioni

# DIGITAL BUILDING BLOCKS FOR TELECOMMUNICATION SYSTEMS

# NICOLA PETRA

Il coordinatore del Corso di Dottorato Ch.mo Prof. Giovanni POGGI

Il Tutore Ch.mo Prof. A.G.M. STROLLO

Anno Accademico 2005-2006

| Chapter   | 1 Introduction                                | 1   |

|-----------|-----------------------------------------------|-----|

| 1.1       | Emerging Trends in Telecommunications Systems | 1   |

| 1.2       | Research Topics                               | 2   |

| 1.3       | Thesis Outline                                | 3   |

| 1.4       | PUBLICATIONS                                  | 3   |

| Chapter   | 2 Signal Processing                           | 6   |

| 2.1       | Direct Digital Frequency Synthesis            | 6   |

| 2.2       | Digital Mixer                                 | 25  |

| 2.3       | Rectangular to Polar                          | 44  |

| 2.4       | Interpolator for Digital Modems               | 58  |

| Chapter   | 3 Forward Error Correction                    | 69  |

| 3.1       | Galois field Multipliers                      | 69  |

| 3.2       | Reed-Solomon Decoder                          | 96  |

| Chapter 4 | 4 VLSI Design                                 | 104 |

| 4.1       | Sense Amplifier Flip-Flop                     | 104 |

| 4.2       | Truncated Multipliers                         | 122 |

| Appendi   | x A: DDFS                                     | 138 |

| Appendi   | x B: GF                                       | 140 |

| Reference | es                                            | 143 |

# Acknowledgments

I would like to give my most sincere thanks to my tutor, professor Antonio Strollo. His experience, knowledge, scientific methodology have been a constant example for me. His enthusiasm, support, and willingness in sharing his invaluable experience have been the stimulus at the basis of my activity as a Ph.D. student.

I want to thank the professors of the Electronics Group at the University of Napoli, for their priceless lessons.

I also want to thank the professor Alan Willson. The Wednesday talks gave me insights, stimulus and ideas I will always remember.

A great thank goes to the friends of the department of Electronics and Telecommunications Engineering, Davide, Ettore, Enzo, Fabrizio, Francesco, Dino, Luigi, Ilaria, for their support and friendship. Most of my passion for electronics comes from the opportunity to work with such wonderful people.

Many other people deserve my thanks for they, in many ways, helped me in the years of my Ph.D. study. A small, possibly incomplete list is: Luca, Paola, Giandomenico, Ciccio, Ferdinando, Teresa, Alessia, Alessandro, Ana, Ricki, Guichang, RuGang, Kate.

The final, most important thank, goes to my family. They are my strength, my pride, my joy.

# Chapter 1 Introduction

# 1.1 Emerging Trends in Telecommunications Systems

In the recent years there is a growing trend in the communication technologies to shift from analogue toward digital techniques. The use of digital techniques, in fact, overcomes many analogue hardware limitations (like high sensitivity to process and temperature variations, difficult portability as the VLSI technology scales down etc.). Moreover, the programmability offered by digital techniques provides flexibility that is especially important in the context of rapidly evolving communication standards.

Owing to advances in CMOS circuit performances, digital techniques are today able of handling Intermediate Frequency (IF) or even low Radio Frequency (RF) tasks.

Several companies are working in the direction to implement the largest part of their transceivers with a digital approach, using analogue design techniques only for RF front-ends.

Even though the technology is ready to face the challenge of the implementation of digital transceiver, the design techniques still lack in many aspects. For this reason in the last years several technical papers have been published on the issues related to the efficient implementation of digital building blocks for telecommunication systems.

The field of digital electronics for telecommunications is very wide. Nevertheless some specific characteristic are highly desirable in almost all the digital circuits used in the modern transceiver.

The first characteristic is the speed. In order to operate at IF, digital circuits for telecommunications must be able to operate with clocks running at frequencies of hundreds of megahertzs.

The second important characteristic is the power dissipation. As a matter of fact, due to the high diffusion of wireless transceivers (used

in notebooks, PDAs, cell phones, etc.) the power dissipated by every building block of the transceiver must be as low as possible.

In order to match these two requirements, the design of a high-performance building block for telecommunication systems must go through subsequent optimization stages.

At the highest level, the analytical description of the functionality of the circuit must be optimized in order to reduce the hardware architecture needed to implement the computation. This is possibly the main difference between the building blocks proposed in *Literature*. An efficient definition of the analytical computation in a digital domain can indeed highly reduce the power dissipation of the circuit and increase its operating speed.

Gate and transistor level design techniques can be developed to further improve the performance of the circuits.

As a final note, since the emerging possibilities of digital VLSI circuits are related to the advance in technology, experimental verification of the performance of a digital building block for telecommunication systems is not an option. It is hence important to verify the performance of a digital circuit for telecommunication through experimental analysis of fabricated prototypes.

# 1.2 Research Topics

On the basis of the emerging trends in telecommunications, my research activity is based on the design and the optimization of digital building blocks for telecommunication systems. The field of telecommunication circuits is very wide. My Ph.D. research activity has been focused on two main topics.

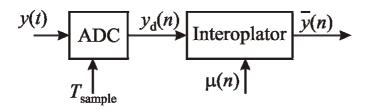

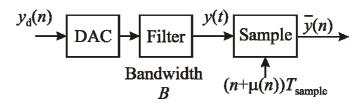

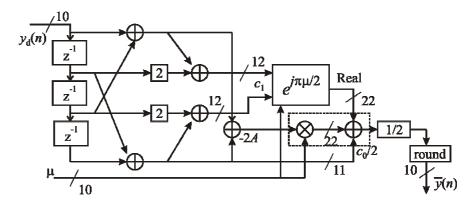

The first topic is the efficient design of digital circuits for signal processing at intermediate and base band. In this category I have worked to the development of new architectures for Direct Digital Frequency Synthesizers (DDFSs), Direct Digital Frequency Synthesizers/Mixers (DDFSMs), Cartesian to Polar coordinates converters and Interpolators for digital modems. These are the main blocks for the processing of the signals elaborated by the analogue front-end. They are used to generate sinusoids waveforms, to make up/down conversion, to change the sample frequency in the digital

domain and to implement a large family of computations used in digital modulation schemes.

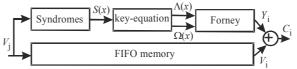

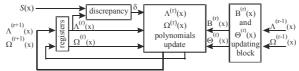

The second topic is the development of new architectures for Reed-Solomon Decoders. Even though the scheme of the Reed-Solomon decoding procedure has been developed more than forty years ago, efficient implementation of the decoding circuit and its sub-circuits is still a topic of main concern.

### 1.3 Thesis Outline

This thesis is organized as follows.

The chapter two synthesizes my research activity focused on the development of efficient architectures for signal processing. The chapter two is divided in four sections focused on the implementation of DDFSs, DDFSMs, Cartesian to Polar converter and Digital Interpolator respectively.

The chapter three synthesizes my research activity on the implementation of Reed-Solomon decoders. The first section of the chapter describes a new architecture for Galois fields multipliers, whereas the second section describes a new architecture for Reed-Solomon decoder.

In the chapter four the results obtained in the development of high-performance Flip-Flop and Truncated multipliers is discussed. These two circuits are not used only in the design of building blocks for telecommunications, but are of main relevance in the design of digital VLSI circuits. Nevertheless, the results achieved in the development of the two mentioned circuits had a high impact on the development of the other circuits.

#### 1.4 Publications

• A.G.M. Strollo, N. Petra, D. De Caro, "Dual-tree error compensation for high performance fixed-width multipliers", *IEEE Transactions on Circuits and System II*, vol.52, no.8, pp.501-507, Aug.2005.

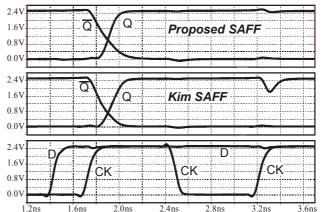

- A.G.M. Strollo, D. De Caro, E. Napoli, N. Petra, "A Novel High-Speed Sense Amplifier based Flip-flop", *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, vo.13, no.11, pp.1266-1274, Nov.2005.

- A.G.M. Strollo, N. Petra, D. De Caro, E. Napoli, "Fixed-width Multipliers with Dual-tree Error Compensation", 16th European Conference on Circuits Theory and Design (ECCTD 2003), Krakow (Poland), Sept.1-4 2003.

- A.G.M. Strollo, D. De Caro, N. Petra, E. Napoli, "True Random Number Generator based on LFSR sampling", 16th *European Conference on Circuits Theory and Design* (ECCTD2003), Krakow (Poland), Sept.1-4 2003.

- A.G.M. Strollo, N. Petra, D. De Caro, E. Napoli, "VLSI Design of a (255,239) Reed-Solomon Decoder", 16th European Conference on Circuits Theory and Design (ECCTD 2003), Krakow (Poland), Sept.1-4 2003.

- A.G.M. Strollo, D. De Caro, E. Napoli, N. Petra, "Direct Digital Frequency Synthesis with Dual-slope Approach", 29th *European Solid-State Circuits Conference* (ESSCIRS 2003), Estoril (Portugal), Sept. 16-18 2003.

- A.G.M. Strollo, D. De Caro, E. Napoli, N. Petra, "High-speed Direct Digital Frequency Synthesizers in 0.25-um CMOS", Proc. of *IEEE Custom Integrated Circuits Conference* (CICC2004), Orlando (USA), Oct.3-6 2004.

- A.G.M. Strollo, N. Petra, D. De Caro, E. Napoli, "An Area-Efficient High-Speed Reed-Solomon Decoder in 0.25um CMOS", 30th *European Solid-State Circuits Conference* (ESSCIRC 2004), Leuven (Belgium), Sept. 20-24 2004.

- D. De Caro, E. Napoli, N. Petra, A.G.M. Strollo, "A High-Speed Sense-Amplifier based Flip-flop", 30th *European Conference on Circuits Theory and Design* (ECCTD 2005), Cork (Ireland), 2005.

- D. De Caro, N. Petra, A.G.M. Strollo, "A 630MHz Direct Digital Frequency Synthesizer with 90dBc SFDR in 0.25um CMOS", Proc. of *IEEE International Solid-State Circuit* Conference 2006, San Francisco, USA, pp.256-257, Feb.2006.

- D. De Caro, N. Petra, A.G.M. Strollo, "A 380MHz, 150mW Direct Digital Synthesizer/Mixer in 0.25um CMOS", Proc. of

- *IEEE International Solid-State Circuit Conference* 2006, San Francisco, USA, pp.258-259, Feb.2006.

- D. De Caro, N. Petra, A.G.M. Strollo, "A 380MHz Direct Digital Synthesizer/Mixer with Hybrid CORDIC Architecture in 0.25um CMOS", *IEEE Journal of Solid State Circuits*, Volume 42, Issue 1, January 2007.

- A.G.M. Strollo, D. De Caro, N. Petra, "A 630MHz, 76mW, Direct Digital Frequency Synthesizer Using Enhanced ROM Compression Technique", *Journal of Solid State Circuits*, Volume 42, Issue 2, February 2007.

# **Chapter 2 Signal Processing**

# 2.1 Direct Digital Frequency Synthesis

Direct Digital Frequency Synthesizers (DDFSs) compute single-phase or quadrature sinusoids with excellent frequency resolution, good spectral purity, very fast frequency switching and phase continuity on switching [1]-[4]. Typical applications include modern communication systems (including spread-spectrum and frequency hopping systems) and measurement instrumentations.

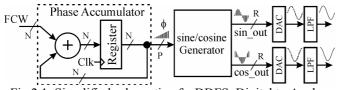

As shown in Fig. 2.1, a quadrature DDFS is basically composed by the series of a phase accumulator and a sine/cosine generator. Analog outputs, when needed, are obtained by using DACs followed by low-pass reconstruction filters.

The phase accumulator is an overflowing N-bit accumulator that produces a digital sweep with a slope imposed by the value FCW of the frequency control word. The frequency  $f_{out}$  of generated signals is proportional to FCW and is given by

$$f_{out} = \frac{FCW}{2^N} f_{clk}; \quad 0 \le FCW \le 2^{N-1}$$

(2.1)

where  $f_{clk}$  is the clock frequency.

The most critical block in a DDFS is the sine/cosine generator. In the simplest implementation, the output of the accumulator addresses a read only memory (ROM). The ROM implements a big lookup table storing *R*-bit digitized sine and cosine waveforms. To reduce the ROM size, the phase value passed to the sine-cosine generator is normally truncated to *P*-bits. Phase truncation introduces spurious

Fig.2.1. Simplified schematic of a DDFS. Digital to Analog Converter and Low-Pass Filter are included when analog output are needed.

noise in the DDFS outputs, and the P value is chosen [5]-[7] according to the required Spurious Free Dynamic Range (SFDR). The lookup table size is also typically reduced by storing sine and cosine values only for angles in  $[0, \pi/4)$ . Output values for the full range  $[0, 2\pi)$  of input phase are generated by exploiting the quarter-wave symmetry of trigonometric functions and trigonometric identities. Using both phase truncation and quarter wave symmetry, the total ROM size is:  $(1/4)R\cdot 2^P$  bits. This value is usually prohibitive for high-speed and low-power implementations. For instance, a DDFS with 90dBc SFDR uses R=13 and P=16, with a total ROM size larger than  $2.1\times 10^5$  bit.

For this reason, several alternative approaches for the implementation of the sine/cosine generator have been proposed. A comprehensive review has been recently published in [8]. Roughly speaking, proposed algorithms can be subdivided in three categories.

Angle rotation techniques (including CORDIC algorithm and its modifications) [9]-[14], basically, start from a vector in the complex plane for which sine and cosine values are known, and proceed with coordinate rotations until an angle sufficiently close to the desired angle is reached. These techniques use very small look-up memories, but require complex arithmetic circuitry. Some of the angle rotation techniques [12]-[14], give the possibility to realize a Direct Digital Synthesizer/Mixer (DDFSM). A DDFSM rotates an input vector in the complex plane by an angle linearly increasing with time and is, therefore, able to modulate both the output frequency and amplitude. A DDFSM reduces to a DDFS when the input vector is kept constant. However, if only frequency modulation is required, a DDFSM circuit, also when realized in a very effective way [14], results in much larger silicon area and power dissipation when compared to optimized DDFS circuits. Optimized angle rotation techniques for DDFS implementation are proposed in [9]-[11]. The solutions of [9], [10], being based on the CORDIC algorithm, require a large number of cascade rotation stages, and therefore result inherently slow in comparison to other approaches. A state of the art angle rotation technique optimized for DDFS implementation is presented in [11]. In this approach the circuit latency is reduced by employing only two multiplier-based rotation stages.

In polynomial and piecewise polynomial interpolation architectures [15]-[19] a small ROM is used to store polynomial coefficients while

additional arithmetic hardware (multipliers, squarers etc.) is required to implement the polynomial approximation. In some approaches the ROM is eliminated altogether, by using high-order polynomial approximations with hardwired coefficients [16]. However, piecewise linear approximation with optimized coefficients seems a better approach when high speed is required [15], [19]. In fact in this approach the required ROMs can be effectively implemented as random logic, while two simple multiplier-accumulators are required to compute the sine and cosine outputs.

decomposition Angular ROM compression techniques approximations in which the lookup table storing sine values is subdivided in two smaller parts (a "coarse" ROM and a "fine" ROM). The outputs of the coarse and fine ROMs are added together to yield the final sine/cosine values. One of the most effective and more popular algorithms was developed by Nicholas [20]. The DDFS recently presented in [21] uses an improved approach, in which the total ROM size is further reduced by decomposing both coarse and fine ROMs as the sum of an "error" ROM and a "quantization" ROM. In this section ([22], [35]) we will introduce the developed DDFS architecture based on the recently proposed Multipartite Table Method [23]. This method has been found ideally suited for high-performance synthesizers, requiring both very small lookup tables and simple arithmetic circuitry. The algorithm generalizes the Nicholas technique by decomposing the lookup table in  $K \ge 2$  small ROMs, whose outputs are added together to obtain the final result. The content of the ROMs is calculated by optimizing the SFDR. The DDFSs designed with the proposed technique require only small lookup tables and simple multi-operand adders. The circuit developed reaches 90dBc SFDR while using a total ROM size less than 1400 bits. The small ROMs are effectively implemented as random logic, while pipelined tree-based multi-operand adders are employed. An operating frequency of 630MHz was obtained by using a standard-cell design in a 2.5V, 0.25µm CMOS. In order to reduce the power dissipation, we employed a power-driven synthesis and included two flip-flop topologies (with different power and delay performances) in the standard cell library. In this way, a total power dissipation of 76mW at 630MHz was achieved. By reducing the power supply at 1.8V, a maximum operating frequency of 430MHz was measured, with a total power dissipation as low as 24.9mW.

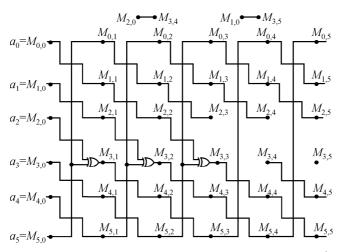

Fig.2.2. Sine/cosine generator architecture.

# 2.1.1 ROM Compression Algorithm

The architecture of the sine/cosine generator block is shown in Fig.2.2. The *P*-bits input signal  $\phi$  represents the input phase  $[0,2\pi)$ . The signal x (obtained from the Q=P-3 less significant bits of  $\phi$ ) represents an angle in  $[0,\pi/4)$ , scaled to a binary fraction in [0,1). The two blocks "sine calculation" and "cosine calculation" in Fig. 2.2 are the heart of the DDFS, and compute:

$$f(x) = Z \sin\left(\frac{\pi}{4}x\right); \quad g(x) = Z \cos\left(\frac{\pi}{4}x\right)$$

(2.2)

where Z is the maximum amplitude of the generated signals, given by:  $2^{R-1}-1$ . The three most significant bits of  $\phi$  determine the octant in which the input phase lies and are input of a decoding logic. The output of the decoding logic are four signals that control the complementing of x, f(x), g(x) and the swapping between f(x) and g(x), needed to properly reconstruct sine and cosine waveforms [1].

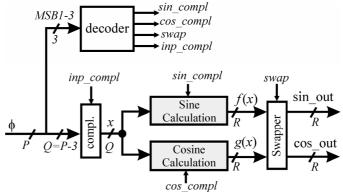

In our circuit the sine and cosine calculation blocks of Fig.2 have been implemented with a Multipartite Table approximation. In order to introduce the Multipartite Table Method (MTM), which is described in detail in [23], let us focus on the sine calculation block (which approximates f(x) function) in Fig.2.2. In MTM the Q-bit input signal x is decomposed in K+1 non overlapping sub-words:  $x_0, x_1, x_K$  of lengths  $q_0, q_1... q_K$  respectively. Hence the value of the input operand is:  $x = x_0 + x_1 + ... + x_K$  and the length is:  $Q = q_0 + q_1 + ... + q_K$ . A piecewise linear approximation of f(x) can be written as:

Fig. 2.3. Implementation of the Multipartite Table Method using two Table of Offsets (*K*=2). *a*) Straightforward implementation of the MTM for *K*=2.

b) Reduced complexity implementation obtained exploiting symmetry of the TOs values.

$$f(x) = f(x_0 + x_1 + \dots + x_K)$$

$$\approx A(x_0) + B(x_0) \cdot (x_1 + \dots + x_K)$$

$$= A(x_0) + B(x_0) \cdot x_1 + \dots + B(x_0) \cdot x_K$$

(2.3)

where the interval [0,1) of x has been divided in  $2^{q_0}$  subintervals, the quantity  $x_0$  represents the starting point of each subinterval and x 1+...+ $x_K$  is the offset in each interval between x and  $x_0$ .

The term  $B(x_0) \cdot x_1$  is then approximated as  $B_1(\xi_1) \cdot x_1$ , where  $\xi_1$  is a sub-word of  $x_0$  including its  $p_1 \le q_0$  most-significant bits. Likewise the term  $B(x_0) \cdot x_2$  is approximated as  $B_2(\xi_2) \cdot x_2$ , where  $\xi_2$  is a sub-word of  $x_0$  including its  $p_2 \le p_1$  most-significant bits. Similar approximation can be done for the terms  $B(x_0) \cdot x_i$  (i=3...K). The equation (2.3) becomes:

$$f(x) \simeq A(x_0) + B_1(\xi_1) \cdot x_1 + B_2(\xi_2) \cdot x_2 + \dots + B_K(\xi_K) \cdot x_K$$

(2.4)

In this equation, the term  $A(x_0)$  is realized with a ROM (named Table of Initial Values, TIV) with  $2^{q_0}$  entries. Similarly, the terms  $B_i(\xi_i) \cdot x_i$  (i=1,...,K) are implemented with K ROMs (Table of Offsets, TO<sub>i</sub>) with  $2^{p_i+q_i}$  entries each (see Fig.2.3a). In [23] it is shown that the Tables of Offsets can be made symmetric. In this way the Tables of Offsets can be reduced in size by a factor of two, at the expense of a few XORs, as shown in Fig.2.3b.

The values to be stored in the ROMs are obtained by using the min-max approach (see [23]). For completeness, the formulas to calculate ROMs content and size are reported in the Appendix A, by particularizing the approach of [23] to DDFS application.

For a given value of K, the optimal decomposition  $\mathcal{D}_f = \{q_0, q_1, p_1, ..., q_K, p_K\}$  is defined in [23] as the one that allows to

minimize the total memory size, while fulfilling the accuracy requirement known as *faithful rounding* (the returned result is one of the two fixed-point numbers closest to the exact value of f(x)).

For a quadrature DDFS two (possibly different) decompositions should be obtained for the two functions f(x) and g(x) in (2.2). We indicate as  $\mathcal{D}_T = \{\mathcal{D}_f, \mathcal{D}_g\}$  the total DDFS configuration. Moreover, faithful rounding is not required in DDFS, where the error metric is the SFDR. As shown in [15] locally increasing the approximation error may, in some cases, result in improved spurious performances. Moreover, relaxing the specification on the local approximation error, a substantial memory saving can be achieved with respect to a faithful rounding approach (see Tab.2.2 in the following).

Therefore we developed a novel algorithm to find the optimal decomposition  $\mathcal{D}_T = \{\mathcal{D}_f, \mathcal{D}_g\}$  which minimizes the ROM size while achieving a specified SFDR. Our algorithm, shown in Fig.2.4, considers only the case in which the same value of K is used in both  $\mathcal{D}_f$  and  $\mathcal{D}_g$ . Moreover it assumes that, for a given decomposition, the lookup tables' content is evaluated in order to minimize the maximum approximation error (see appendix A). The algorithm includes three main steps. A time-consuming search is performed in the final step, while the first two steps of the algorithm are aimed to reduce the search space. Two parameters are introduced in the first two steps. The maxROM parameter limits the maximum ROM size of each considered decomposition. Since the algorithm is aimed to find the solution with the minimal ROM size, the parameter maxROM does not affect the final calculated solution and is included only to reduce the search space. The second parameter is the maximum approximation error  $\varepsilon_{max}$  of each considered decomposition. This parameter allows not only to reduce the search space, but also to find solutions which match a constraint on both the SFDR and the maximum approximation error.

In the first step of the algorithm, for the prescribed K value, all the possible decompositions for the input x are enumerated. Each decomposition which is acceptable to implement f(x) is saved. A decomposition  $\mathcal{D}_f$  is considered acceptable if the approximation error is smaller than  $\varepsilon_{max}$  and the size of the ROM for the computation of f(x) is smaller than  $0.75 \cdot maxROM$ . Similarly, each decomposition  $\mathcal{D}_g$

```

set Nsin=0: Ncos=0: Nt=0:

enumerate all the N possible input decomposition \mathcal{D}(i);

for h in 1 to N

if \mathcal{D}(h) is acceptable for f(x) then

(the decomposition is considered acceptable if the approximation error

is smaller than \varepsilon_{max} and the ROM size is smaller than 0.75 \times maxROM)

set: Nsin = Nsin +1; \mathcal{D}_{f}(Nsin) = \mathcal{D}(h);

if \mathcal{D}(h) is acceptable for g(x) then

set: N\cos = N\cos +1; \mathcal{D}_q(N\cos) = \mathcal{D}(h);

end if

end for

for i in 1 to Nsin and for i in 1 to Ncos

if \{\mathcal{D}_f(i),\,\mathcal{D}_g(j)\} is acceptable for DDFS implementation then

(the set of the two decompositions is acceptable if the total ROM size is

smaller than maxROM and the values of q0, q1, q2... are the same in

\mathcal{D}_{\mathbf{f}}(i) and \mathcal{D}_{\mathbf{g}}(j)

set: Nt = Nt + 1; \mathcal{D}_T(Nt) = {\mathcal{D}_f(i), \mathcal{D}_g(j)};

end if

end for

sort \mathcal{D}_T in ascending order of the total ROM size;

for i in 1 to Nt

Calculate SFDR assuming \mathcal{D}_{\text{T}} as DDFS configuration;

if (SFDR > target_SFDR - \Delta) then

Perform "amplitude optimization"

if (final_SFDR >= target_SFDR) then

Optimal solution found; exit program

end if

end if

end for

```

Fig.2.4. Algorithm to determine the optimal MTM decomposition, for a given number of table of offsets. Input parameters are:  $target\_SFDR$  (the required SFDR),  $\varepsilon_{max}$  (the maximum approximation error) and maxROM (the maximum ROM size).

acceptable to implement g(x) is also saved<sup>1</sup>. In spite of the initially large search space, the computation time for this first step is reduced since the approximation error and the ROM size can be calculated according to [23], with simple formulas (see appendix A).

In the second step of the algorithm, all the possible DDFS configuration that can be realized by using the saved f(x) and g(x) decompositions are enumerated. Also in this case, each acceptable DDFS configuration is saved. A DDFS configuration is considered acceptable if the total ROM size (the sum of the size of the ROMs needed to implement both f(x) and g(x)) is smaller than maxROM and, moreover, the values of  $q_0$ ,  $q_1$ ,  $q_K$ ... are the same for f(x) and g(x). This second condition is imposed to simplify the DDFS hardware implementation, as will be detailed in the section 2.1.2.

<sup>&</sup>lt;sup>1</sup> The value 0.75·maxROM has been obtained heuristically. In all our implementations, in fact, the cosine ROM size is always smaller than 0.75·maxROM. The same holds true for the sine ROM size.

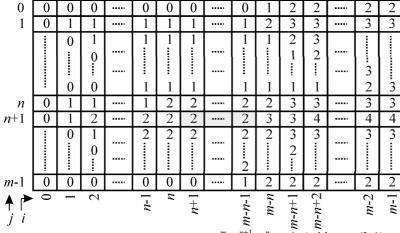

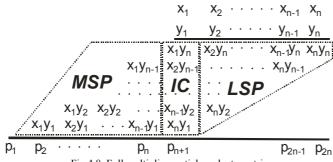

| K | $\mathcal{D}_{\!f}$                                                              | sine<br>ROM | $\mathcal{D}_{g}$                                                                | cosine<br>ROM | total<br>ROM |

|---|----------------------------------------------------------------------------------|-------------|----------------------------------------------------------------------------------|---------------|--------------|

| 1 | $q_0=7; q_1=6, p_1=1$<br>g=0                                                     | 1792        | $q_0=7; q_1=6, p_1=3$<br>g=0                                                     | 2432          | 4224         |

| 2 | $q_0$ =5; $q_1$ =3, $p_1$ =3<br>$q_2$ =5, $p_2$ =2; $g$ =0                       | 768         | $q_0$ =5; $q_1$ =3, $p_1$ =5<br>$q_2$ =5, $p_2$ =1; $g$ =0                       | 1056          | 1824         |

| 3 | $q_0$ =5; $q_1$ =2, $p_1$ =3<br>$q_2$ =3, $p_2$ =3<br>$q_3$ =3, $p_3$ =1; $g$ =0 | 616         | $q_0$ =5; $q_1$ =2, $p_1$ =5<br>$q_2$ =3, $p_2$ =2<br>$q_3$ =3, $p_3$ =1; $g$ =0 | 728           | 1344         |

Tab.2.1. Optimal decompositions for sine and cosine calculation blocks for a DDFS with 90 dBc SFDR, with *R*=13 and *P*=16; g is the number of guard bits.

A final search is performed in the third step of the algorithm. For each saved DDFS configuration, starting from the one with the lowest total memory size and proceeding in ascending ROM size order, the values to be stored in the tables are calculated following [23] (see appendix A) and the SFDR is calculated by numerical simulation. The first solution found that meets the target SFDR is the optimal one, with the minimum ROM size. As can be seen in Fig.2.4, if the SFDR is near to the target value, amplitude optimization is carried-out to improve spectral purity. Amplitude optimization [20] consists in scaling the values to be stored in the lookup tables before rounding, to provide improved performance in the presence of amplitude quantization. To that purpose, a search is performed by varying the amplitude Z in (2.2). For each trial Z value, the content of the lookup tables is calculated and the resulting SFDR is computed. The best amplitude value is selected as the one yielding the largest SFDR. The use of a very small step size (less than one LSB) during the search in Z guarantees a negligible reduction of the output signals amplitude. The value of  $\Delta$  in Fig. 2.4 has been chosen equal to 3dB, which is a SFDR gain which can be reasonably obtained with the amplitude optimization.

The Tab.2.1 shows the optimal DDFS configurations obtained by using one, two or three Tables of Offsets, for a 90dBc SFDR, with R=13 and P=16. Please note that the MSB of the Table of Initial Values of the cosine function is constant, and has not been considered in determining the ROM size values reported in Tab.2.1. As can be seen, even for K=1 the total DDFS ROM size is only a small fraction of the memory size  $(2.1\times10^5 \text{ bits})$  that would be required by using an uncompressed lookup table. The ROM size decreases significantly using K=2, while the additional improvement obtained with K=3 is less evident.

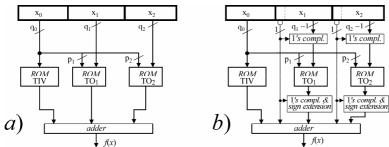

From the above considerations it follows that increasing the number K of Tables of Offsets allows reducing the total memory size. However, any additional table requires the introduction of additional adder inputs and additional complementers, with a trade-off in terms of hardware complexity. Moreover, using more tables increases the approximation and rounding errors (see Appendix A), requiring the introduction of guard bits that may partly overcome the advantages in terms of memory size. By synthesizing many circuits we have found that using K=3 gives a good trade-off between ROM and arithmetic circuit complexity.

The Tab.2.1 also highlights that the optimal solution, given by the algorithm of Fig.2.4, provides two different decompositions for the sine and the cosine functions, with the sine ROM sensibly smaller than the cosine ROM. Actually the error introduced by the MTM approximation depends on the amplitude of the second derivative of the approximated function. Therefore, by using a different decomposition for f(x) and g(x), it is possible to obtain a similar approximation error for the two functions, while reducing the total ROM size.

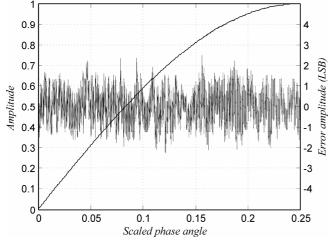

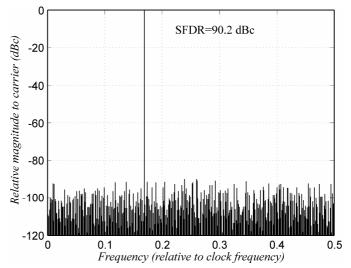

The Fig. 2.5 shows the approximation error for input angles in the first quadrant, for the 90dBc DDFS with K=3. As can be seen, the maximum absolute error is about 2.5 LSB. In spite of the fairly large error in the time domain, the Fig. 2.6 shows that the DDFS is able to reach the required SFDR. This characteristic is common in SFDR

Fig. 2.5. Approximated sine wave and amplitude error, for the 90dBc DDFS with K=3.

optimized DDFS (see [15], [18]).

In this paper, the sine/cosine tables are optimized in the sense of the SFDR metric. The original MTM [23] is based on the faithful rounding requirement. A comparison between the two approaches is presented in Tab.2.2. This comparison is done for R=13, P=16, considering a SFDR constraint (for the proposed approach) of 92.4dBc. This is the maximum possible SFDR for a DDFS with P=16 phase bits.

From Tab.2.2 it can be observed that the proposed approach results in substantial memory saving with respect to the faithful rounded MTM of [23]. The memory saving is close to 40% for K=1, and reaches about 50% for K=3. This improvement is due to the relaxed specification on maximum approximation error.

It is worth to highlight that the SFDR is a long-term averaged metric, while the maximum absolute error is a short-term characteristic. In same applications, especially when the digital output is directly used, it is important to have both long-term and short-term good error characteristics. Our algorithm allows designing DDFS circuits with excellent error characteristics and reduced memory size also in this case. This is possible owing to the presence of the parameter  $\varepsilon_{max}$  (see the algorithm of Fig.2.4) which allows designing DDFS circuits that meet a constraint on both SFDR and maximum absolute error.

The Tab.2.3 shows a comparison between the ROM size and the

Fig.2.6. Output spectrum for the 90dBc DDFS with K=3.  $f_{out}=0.17$ :  $f_{clk}$ .

| Approach                    | K | $\mathcal{D}_f$               | $\mathcal{D}_{g}$                                              | ROM size (b |        | (4D-) |       | max error |

|-----------------------------|---|-------------------------------|----------------------------------------------------------------|-------------|--------|-------|-------|-----------|

|                             |   |                               |                                                                | sine        | cosine | total | (ubc) | (LSB)     |

| This paper                  | 1 | $q_0=7; q_1=6, p_1=2,$<br>g=0 | $q_0=7; q_1=6, p_1=3,$<br>g=0                                  | 2048        | 2432   | 4480  | 92.4  | 1.71      |

|                             | 2 |                               | $q_0-6; q_1-2, p_1-4$<br>$q_2=5, p_2=2; g=0$                   | 1040        | 1024   | 2064  | 92.4  | 2.02      |

|                             | 3 | $q_2=2, p_2=2$                | $q_0=5; q_1=2, p_1=5$<br>$q_2=2, p_2=3$<br>$q_3=4, p_3=1; g=0$ | 704         | 752    | 1456  | 92.4  | 2.35      |

| Faithful<br>rounded<br>[23] | 1 | $q_0=8; q_1=5, p_1=2$<br>g=1  | $q_0=8; q_1=5, p_1=3$<br>g=1                                   | 3584        | 3840   | 7424  | 92.4  | 0.92      |

|                             | 2 |                               | $q_0=6; q_1=3, p_1=5$<br>$q_2=4, p_2=3; g=2$                   | 1472        | 1856   | 3328  | 92.4  | 0.99      |

|                             | 3 | $q_2=2, p_2=2$                | $q_0=6; q_1=2; p_1=5$<br>$q_2=3, p_2=3$<br>$q_3=2, p_3=1; g=2$ | 1408        | 1412   | 2820  | 92.4  | 0.99      |

Tab.2.2. Comparison between DDFS circuits designed by using the proposed algorithm and the faithful rounded approach of [23].

In all circuits R=13 and P=16; g is the number of guard bits.

arithmetic circuits employed in several published DDFS architectures with SFDR values ranging from 80 to 100 dBc. As it can be seen, the optimized MTM approach compares favorably with CORDIC-based architectures that, while requiring less memory, are plagued by the need of many arithmetic circuits. A similar consideration applies to the ROM-less third-order polynomial approximation technique proposed in [16]. Piecewise-linear approximation techniques (represented by [15], [18] in Tab.2.3) need slightly less memory with respect to the proposed technique, but require multipliers (or equivalent circuitry) that easily becomes a speed bottleneck when high clock frequency is required.

The comparison of our DDFS with the ROM compression approaches highlights that the DDFS of [24] requires a 38% smaller ROM size. However the circuit of [24] achieves an 85dBc SFDR and needs two multipliers. The DDFS of [25] reaches a 6 dB larger SFDR in comparison to our circuit, while requiring a larger ROM size and, again, the need of two multipliers. A comparison with the recently proposed Yang technique [21] shows that the proposed approach requires reduced memory size, while using higher phase and amplitude resolutions.

| Reference        | Approx. technique                                       | Phase<br>Resolution<br>, P | Amplitude Resolution, R | SFDR (dBc) | ROM (bits) | Output       | Arithmetic<br>Circuits                              |

|------------------|---------------------------------------------------------|----------------------------|-------------------------|------------|------------|--------------|-----------------------------------------------------|

| Proposed [35]    | Multipartite Table with SFDR optimization, <i>K</i> =3  | 16                         | 13                      | 90.2       | 1344       | quadrature   | 2 multi-<br>operand<br>adders                       |

| Madisetti [9]    | Modified<br>CORDIC                                      | 22                         | 16                      | 100        | 572        | quadrature   | $\pi/4$ multiplier, butterfly stages                |

| Song [11]        | Interpolation-<br>based<br>angle rotation               | 18                         | 16                      | 100        | 270        | quadrature   | 6 multipliers,<br>6 adders                          |

| De Caro [16]     | Third-order<br>polynomial<br>approximatio<br>n          | 14                         | 12                      | 80         | 0          | quadrature   | Partial products gen. and sum.                      |

| Langlois [15]    | Piecewise<br>linear<br>interpolation                    | 18                         | 14                      | 96.2       | 1152       | quadrature   | 2<br>multi-operand<br>adders<br>and<br>multiplexers |

| De Caro [18]     | Piecewise<br>linear<br>interpolation                    | 14                         | 12                      | 83.6       | 896        | quadrature   | 2 merged<br>multiply-add<br>units                   |

| Nicholas [20]    | ROM<br>compression:<br>coarse-fine<br>decompositio<br>n | 15                         | 12                      | 90.3       | 3072       | single phase | multi-operand<br>adder<br>(3 operands)              |

| Curticapean [24] | ROM<br>compression:<br>sine addition<br>formulas        | 14                         | 12                      | 85         | 832        | quadrature   | 2 multipliers,<br>2 adders                          |

| Curticapean [25] | ROM<br>compression:<br>sine addition<br>formulas        | 16                         | 16                      | 96         | 2304       | quadrature   | 2 multipliers,<br>2 adders                          |

| Yang [21]        | ROM<br>compression:<br>coarse-fine<br>decompositio<br>n | 14                         | 12                      | ~ 80       | 2176       | single phase | multi-operand<br>adder<br>(6 operands)              |

Tab.2.3. Comparison between ROM size and arithmetic circuits in recently proposed DDFSs.

#### 2.1.2 DDFS Architecture

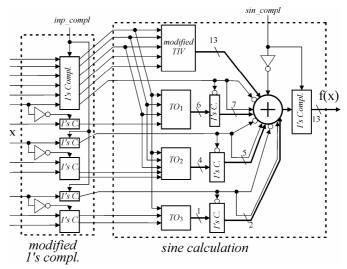

Some optimizations can be carried out when implementing MTM-based DDFSs. As can be seen from the figures 2.2 and 2.3b, some of the address bits of the Tables of Offsets are computed through the cascade of two 1's complementers. These two complementers can actually be replaced by a single modified 1's complementer. Moreover, since our search algorithm imposes the same  $q_0, q_1, ..., q_K$  values for the  $\mathcal{D}_f$  and  $\mathcal{D}_g$  decompositions, an unique modified 1's complementer can be shared for the two blocks, with additional hardware saving. In the following we will focus on the implementation of the 90dBc DDFS, with K=3. The modified 1's complementer for this design, and the detailed architecture of the sine calculation block, are shown in Fig.2.7.

In the Multipartite Table approach the content of the tables of offsets (TOs) has to be conditionally added or subtracted from the value stored in the Table of Initial Values (TIV). The architecture of Fig.2.7 implements this operation by using the sign-extension prevention (SEP) technique [26], in order to reduce the word length of the terms to be summed in the multi-operand adder. In the SEP technique the conditionally complemented offset values (stored in TOs tables) are extended by using a single bit, and suitable sign extension prevention constant (SEPC) is summed to the final result. The SEPC is known beforehand, therefore the SEP technique is implemented by using a modified Table of Initial Values, storing the sum of the "original" Table of Initial Values plus the SEPC.

The SEP technique is also exploited in Fig.2.7 to conditionally 2's complement the output of the sine generator. This is usually performed by firstly performing a 1's complement and then adding 1 LSB:

$$-f = \overline{f} + 1 \tag{2.5}$$

However, it is also possible to compute the 2's complement by firstly subtracting 1 LSB and then performing a 1's complement:

$$-f = \overline{f - 1} \tag{2.6}$$

This is the approach employed in Fig.2.7. Subtracting 1 LSB from f is achieved by applying the SEP technique. Accordingly, the complement of the  $sin\_compl$  signal is included in the final addition and the relevant SEPC is added to the modified Table of Initial Values. For this reason the output word length of the modified Table

Fig.2.7. Schematic of the modified 1's complementer and of the optimized sine generator using sign-extension prevention technique.

of Initial Values is one bit larger than the original Table of Initial Values. This results in a slightly larger memory requirement with respect to the values reported in Tab.2.1 (for instance, the total sine ROM of the circuit in Fig.2.7 increases from 616 to 648 bit). This disadvantage is more than compensated by the simplification in the final multi-operand adder.

## 2.1.3 Power-Driven Flip-Flop Selection

The developed DDFS architecture can easily be pipelined to reach a high clock frequency. When a fine-grain pipeline is employed, the propagation delay of the few logic levels between the pipeline stages is comparable with the amount of clock cycle time taken by the flip-flops. Therefore using a high performance flip-flop is of outmost importance to increase the maximum clock frequency or reduce the number of pipelining flip-flops. When ultimate speed performances are required, using a flip-flop topology with reduced D-Q delay is mandatory and the power dissipation of the large number of pipelining flip-flops represents the main portion of the overall power dissipation. Real designs often include many flip-flops that are not on the critical path. This timing slack can be exploited by using slower, more energy-efficient, flip-flops on the non-critical paths, improving the overall power dissipation [30],[31].

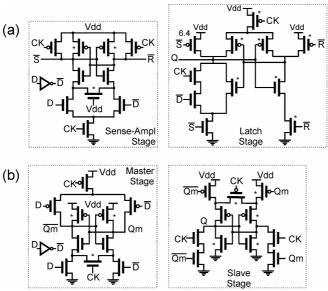

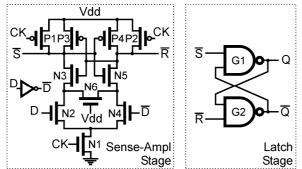

Fig.2.8. Schematic of the flip-flops used for the DDFS implementation.

(a) Imporved Sense-Amplifier based Flip-flop (SAFF);

(b) Static Ratio Insensitive Flip-flop (SRIS)

The asterisk (\*) indicates the minimum sized devices.

A number of novel flip-flop topologies have been recently proposed and figure of merit like Power-Delay (or Energy-Delay) product are often used to determine the "best" topology [29]. When a single flipflop topology is employed, the transistors sizing can be exploited to meet the timing requirements while optimizing the power dissipation. Unfortunately this approach is not optimal for several reasons. First of all, an aggressing transistor downsizing worsens the Power-Delay product [29]. Moreover cells with a very low transistors sizing show a large dependence of the D-Q delay on the output capacitance. This makes timing closure very hard, especially in a standard cell approach, since the exact output parasitics values are known only after the detailed routing. Finally, there is no flip-flop topology with minimal Power–Delay product for any value of the input switching activity. To overcome the limitation of the single flip-flop topology approach, in the design of our IC, we selected two different flip-flop topologies with different speed and power dissipation characteristics. The first flip-flop topology, shown in Fig.2.8a, is the improved Sense-Amplifier based flip-flop (SAFF) introduced in [32], [33] and optimized for a single-ended output. This circuit is one of the fastest

Fig.2.9. Flip-flop Power and D-Q Delay considering different sizing. SAFF is shown in Fig.8a, while SRIS is shown in Fig.8b.

sequential elements available today thanks to the setup time close to zero, given by the Sense-Amplifier stage, and the reduced clock to output delay provided by the Latch stage. Another advantage of this topology is the self-timed sampling window closing mechanism which gives a reduced hold time and an intrinsic robustness against sizing, process, voltage, and temperature variations. In the flip-flop of Fig.2.8a, the  $\overline{S}$  and  $\overline{R}$  exhibits a switching activity close to that of the clock signal, providing a large power consumption, especially in the case of a D input with a low switching activity.

The second flip-flop topology, shown in Fig.2.8b, is the Static Ratio Insensitive (SRIS) flip-flop of Yuan and Svensson [34]. This circuit presents very low power dissipation because of its non-precharged nature and the reduced clock load. The speed is the drawback of this topology because of the large setup time (due to the master/slave configuration), and the two delay stages of the slave latch.

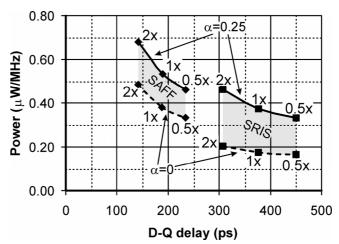

The Fig.2.9 compares the speed and the power dissipation of the two flip-flops considering different circuit sizing (2x, 1x, 0.5x) for a 0.25µm technology. In this figure the switching activity  $\alpha$  is defined as the ratio of the average D frequency and the clock frequency. For  $\alpha$ =0.25 the SAFFs provide a Power-Delay product lower than the SRIS topologies. On the other hand, for  $\alpha$ =0 the best Power-Delay product is obtained with the SRIS topology.

We have implemented the proposed 90dBc DDFS with K=3 by using a standard cell approach, with a 0.25 $\mu$ m, 2.5V technology. The DDFS

| Employed Flip-flops                | Area<br>(10 <sup>3</sup> μm <sup>2</sup> ) | clock freq.<br>(MHz) | $P_D$ ( $\mu$ W/MHz) |

|------------------------------------|--------------------------------------------|----------------------|----------------------|

| SRIS 2x                            | 79.6                                       | 516                  | 147                  |

| SAFF 2x                            | 78.9                                       | 600                  | 216                  |

| SAFF 2x/1x                         | 65.5                                       | 600                  | 176                  |

| SAFF 2x/1x/05x                     | 59.5                                       | 600                  | 157                  |

| SAFF 2x/1x/05x +<br>SRIS 2x/1x/05x | 63.2                                       | 600                  | 130                  |

Tab.2.4. Simulation results for the proposed 90dBc DDFS by employing different flip-flop topologies.

includes a 32-bit accumulator, composed by four pipelined stages, each one of 8 bits. The circuit has been synthesized for a target clock frequency of 600MHz.

The Tab.2.4 shows the performances achieved by synthesizing the proposed DDFS, with different flip-flops sizing and topologies. The required clock frequency is not achieved by using only SRIS flip-flops. By using only SAFFs, the target clock frequency is reached and a reduction of 27% in the power dissipation is observed when several flip-flop sizing are used. By using the two flip-flop topologies together a further 17% power reduction can be obtained without any speed penalty.

# 2.1.4 VLSI Implementations Results

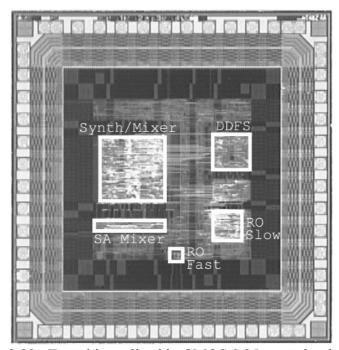

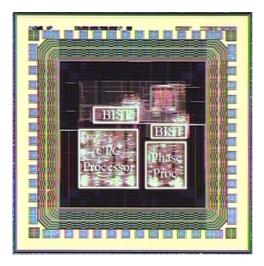

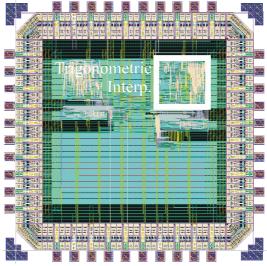

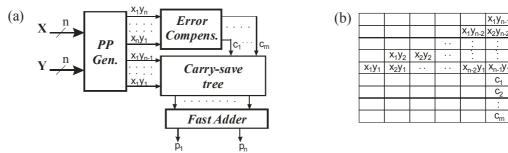

The 90dBc DDFS circuit has been fabricated on a test chip, see Fig.2.10. The circuit includes a built-in self-test structure (BIST Logic) to make easier the measurements of DDFS maximum clock frequency and power dissipation.

The Tab.2.5 reports the experimental performances of the circuit. The DDFS exhibits a maximum operating frequency of 630MHz, with a

| Technology              | 0.25μm 2.5V           | 5M 1P            |

|-------------------------|-----------------------|------------------|

| Die Area                | 0.063 mm <sup>2</sup> |                  |

| Frequency Control Word  | 32 bit                |                  |

| Output Resolution       | 13 bit                |                  |

| SFDR                    | 90 dBc                |                  |

| Maximum Clock Frequency | 630 MHz               | @ 2.5V           |

| Maximum Clock Frequency | 430 MHz               | @ 1.8V           |

| Frequency Resolution    | 0.15 Hz               | @ 630 MHz        |

| Power Dissipation       | 76.2 mW               | @ 2.5V - 630 MHz |

| Fower Dissipation       | 24.9 mW               | @ 1.8V - 430 MHz |

|                         |                       |                  |

Tab.2.5. Experimental performances of the proposed IC.

Fig.2.10. Test chip micrograph.

total power dissipation of 76mW at 630MHz. By reducing the power supply at 1.8V, a maximum operating frequency of 430MHz was measured, with a total power dissipation of only 24.9mW.

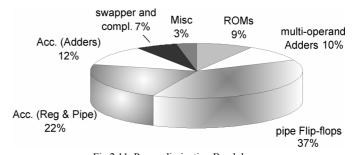

The Fig.2.11 shows the simulated power breakdown of the proposed DDFS. It is interesting to observe that the flip-flop power dissipation is close to the 60% of the total power. The power dissipation of the accumulator is not negligible, while the sine and cosine computation logic requires about the 56% of the total power. The power contribution of the lookup tables is very low (9%).

The data shown in Tab.2.6 compare the performances of the developed DDFS with the ones of some recently published state of the art circuits, using CMOS technology, SFDR and clock frequency similar to the ones considered in this paper. The developed DDFS uses only a fraction of the area of previous circuits. Comparing with our

Fig.2.11. Power dissipation Breakdown.

| Circuit                    | Technique                                   | Accum.<br>(bit) | SFDR<br>(dBc) | Pipeline<br>levels | Output                | Process<br>(μm) | Area<br>(mm²) | fclk max<br>(MHz) | Power<br>(μW/MHz) |

|----------------------------|---------------------------------------------|-----------------|---------------|--------------------|-----------------------|-----------------|---------------|-------------------|-------------------|

| This paper                 | Multipartite table with SFDR opt.           | 32              | 90            | 5                  | 13 bits<br>quadrature | 0.25            | 0.063         | 630               | 121               |

| Strollo [19]<br>JSSC 2005  | Dual-slope Piecewise linear (128 segments)  | 24              | 80            | 6                  | 12 bits<br>quadrature | 0.25            | 0.090         | 600               | 120               |

| Langlois [27]<br>CICC 2003 | Piecewise linear<br>(32 segments)           | 32              | 84            | 4                  | 12 bits<br>quadrature | 0.18            | 0.090         | 150               | 600               |

| Song [11]<br>TVLSI 2004    | Interpolation based<br>angle rotation       | 32              | 100           | 9                  | 16 bits<br>quadrature | 0.35            | 1.400         | 150               | 2333              |

| Song [28]<br>JSSC 2004     | Piecewise linear<br>(128 segments)          | 30<br>ΣΔ        | 110           | -                  | 14 bits single        | 0.25            | 0.120         | 250               | 400               |

| Yang [21]<br>JSSC 2004     | ROM Compression:<br>quad-line approximation | 32              | ~ 60          | 26                 | 9 bits<br>single      | 0.35            | 0.440         | 820               | 153               |

| De Caro [14]<br>JSSC 2007  | Hydrid-CORDIC<br>DDFSM circuit              | 32              | 90            | 5                  | 13 bits<br>quadrature | 0.25            | 0.220         | 385               | 400               |

Tab.2.6. Comparison with recently proposed DDFS IC realizations.

previous implementation of [19], this novel IC allows maintaining about the same maximum clock frequency and power dissipation, while providing increased SFDR and a larger accumulator. The DDFS of [21] dissipates 25% more power and is faster than our IC. However, the output resolution and the SFDR of [21] are lower than our design. Moreover two parallel sine generators are used in [21] to increase the maximum clock frequency, with a large area penalty. The proposed IC exhibits a reduction of the power dissipation by a factor larger than 3 and a substantial increase of the maximum clock frequency, with respect to the solutions proposed in [27]-[28].

The last row in Tab.2.6 corresponds to the DDFSM circuit that we have proposed in [14]. The Tab.2.6 highlights that a state of the art DDFSM provides significantly lower performances with respect to optimized DDFS circuits. This is the price to be paid to have both frequency and amplitude output modulations.

#### 2.1.5 Conclusions

The implementation of a high performance DDFS IC based on a Multipartite Table Method has been described. The circuit has been optimized at the architectural and transistor levels. At the architectural level, for the first time, the Multipartite Table approach has been employed to implement a DDFS. At the transistor level two different flip-flop topologies with different power and delay characteristics are used to optimize the circuit performances. The implemented DDFS exhibits large clock frequency and reduced power dissipation.

# 2.2 Digital Mixer

The Direct Digital Frequency Synthesizer/Mixer (DDFSM) is in ubiquitous use for many communication subsystems such as tuners, derotators, up and down frequency converters etc.. In addition, the quadrature mixer is the front-end of various modulation/demodulation schemes, such us BPSK (Binary Phase Shift Keying), QPSK (Quadrature Phase Shift Keying) and QAM (Quadrature Amplitude modulation).

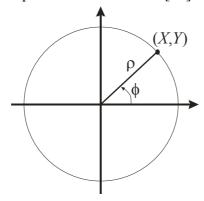

The inputs of a DDFSM are two signals  $X_{in}$  and  $Y_{in}$ , and a frequency control word  $f_{CW}$ . The outputs of the system are computed according to the following equations:

$$\begin{cases} X_{out}(n) = X_{in}(n) \cdot \cos[\theta(n)] - Y_{in}(n) \cdot \sin[\theta(n)] \\ Y_{out}(n) = X_{in}(n) \cdot \sin[\theta(n)] + Y_{in}(n) \cdot \cos[\theta(n)] \end{cases}$$

(2.7)

where:

$$\theta(n) = \omega \cdot n = 2\pi \cdot f_{CW} \cdot n \tag{2.8}$$

The equations (2.7),(2.8) correspond to a complex multiplication between an input vector in the complex plane, with coordinates  $[X_{in}(n), Y_{in}(n)]$ , and a unitary modulus vector  $e^{j\theta}$ :  $X_{out} + jY_{out} = (X_{in} + jY_{in}) e^{j\theta}$ .

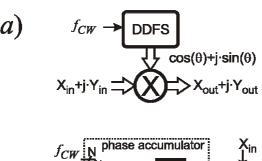

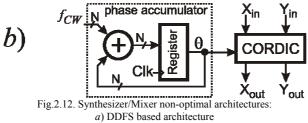

A first implementation for the DDFSM includes two distinct functional units [55], see Fig.2.12a. The first one is a Direct Digital Frequency Synthesizer (DDFS) [56], [57] that generates the sequences  $\sin(2\pi \cdot f_{CW} \cdot n)$  and  $\cos(2\pi \cdot f_{CW} \cdot n)$ . The second one is a complex multiplier, which uses four real multipliers, one adder and one subtractor to generate the outputs  $X_{out}(n)$  and  $Y_{out}(n)$  according to (2.7). This implementation is generally non-optimal [58], [62]. The DDFS is in fact a cumbersome circuit itself. Moreover, the complex multiplier does not exploit the property that the modulus of one of the inputs  $(e^{j\theta})$  is unitary.

A second possible implementation [59], [60] employs a simple overflowing accumulator that generates the angle  $\theta$  and a rotator using the CORDIC algorithm [61] to implement the equations (2.7), see Fig.2.12b. Unfortunately, the CORDIC algorithm in its standard

b) CORDIC based architecture

implementation is inherently slow, using many cascade computation stages.

The recent approaches [62]-[65] overcome the limitations of the simple architecture of Fig.2.12 by implementing Synthesizer/Mixer as the cascade of two stages: a "coarse angle rotation" followed by a "fine rotation stage". In [62]-[64] both the coarse rotation and the fine rotation employ a multiplier based architecture, while the approach of [65] uses a CORDIC architecture for the coarse rotation and a multiplier based fine rotation. The IC implementations [62], [64] are very effective, with a high speed operation and reduced hardware complexity. Until now, no IC implementation exists of the mixed approach of [65].

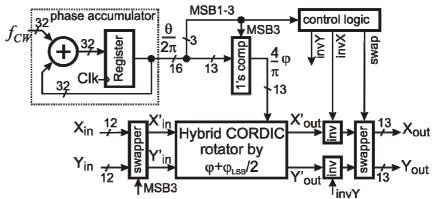

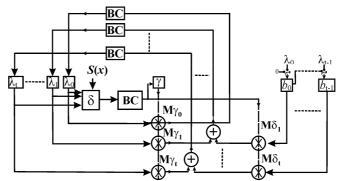

This section ([66], [89]) introduces a novel combined approach, named Hybrid CORDIC, to realize a Synthesizer/Mixer. This approach splits the rotation required in the Synthesizer/Mixer circuit in three rotations. A first rotation is performed by employing a CORDIC datapath in which the rotation directions are computed in parallel, by employing a lookup table. The second rotation is also CORDIC based, with rotations directions computed in parallel analytically. The final (third rotation) is multiplier based.

The parallel evaluation of the rotations directions allows an efficient use of the Carry Save arithmetic in the CORDIC datapath of the first two rotation blocks, without requiring additional Carry Propagate adders (as in [73],[74]) or the introduction of additional CORDIC sub-rotations (as in [75]). The final multiplier based rotation allows

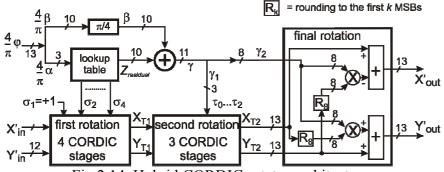

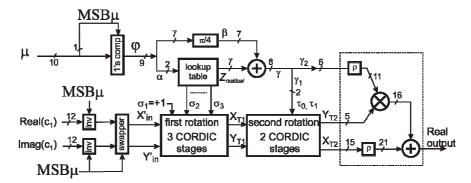

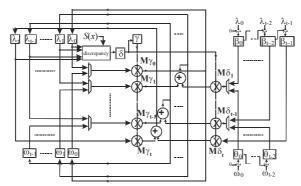

Fig.2.13. Top-level architecture of the designed DDFSM IC.  $\phi_{LSB}$  is given by  $(\pi/4) \cdot 2^{-13}$ .

reducing the overall number of pipelining levels and the circuit complexity as well.

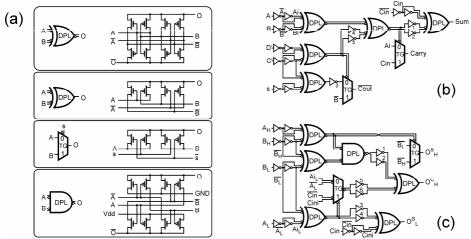

At the transistor level, a novel approach, which combines full-CMOS and Double-Pass-Transistor logic (DPL) [84] design styles, is presented to implement the CORDIC datapath.

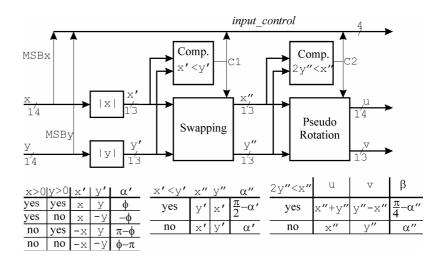

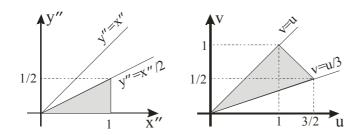

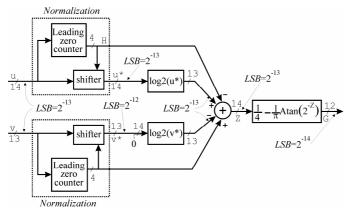

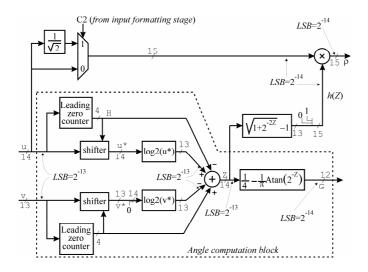

# 2.2.1 Synthesizer/Mixer Basic Architecture

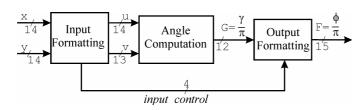

The top-level architecture of the designed DDFSM IC is shown in Fig.2.13. The circuit is sized in order to exhibit a 90dBc Spurious Free Dynamic Range (SFDR). The input word-length is 12 bit while output word-length is 13 bit. The 32 bit phase accumulator generates the rotation angle  $\theta \in [0,2\pi]$ , represented with a binary fractional value in [0,1]. The rotation angle  $\theta$  is truncated to 16 bit, introducing output spurs that are below the 90dBc SFDR constraint. The hearth of the circuit is the Hybrid CORDIC rotator block. This block is able to perform a rotation by an angle  $\phi \in [0,\pi/4]$  represented with a binary fractional value in [0,1]:

$$\frac{4}{\pi} \varphi = f_1 \cdot 2^{-1} + \dots + f_{13} \cdot 2^{-13}$$

(2.9)

The less significant bit of  $\varphi$  has a weight that will be indicated in the following as  $\varphi LSB = (\pi/4) \cdot 2^{-13}$ .

The other minor subsystems in Fig.2.13 (1's complementer, swappers and 2's complementers controlled by control logic) employ the sine and cosine functions symmetries [62], [64] to perform the complete rotation in the full  $[0,2\pi]$  interval. It is worth to highlight that the

Fig.2.14. Hybrid CORDIC rotator architecture

introduction of a  $\varphi$ LSB/2 phase shift in the rotator block, allows to completely eliminate [56], [57], [70] the error due to the employ of a simple 1's complementer to evaluate the angle  $\varphi$ .

# 2.2.2 Hybrid cordic rotator algorithm

The architecture of the Hybrid Cordic rotator is shown in the Fig.2.14. The circuit rotates its input vector  $[X'_{in}, Y'_{in}]$  by the angle  $\varphi+\varphi_{LSB}/2$ . The rotation is performed in three steps. The first two steps are performed with a CORDIC datapath, while the final step is realized by using two multipliers.

### 2.2.3 First rotation

In the first step, the angle  $\varphi$  is divided in two sub-words:  $\varphi = \alpha + \beta$ , where:

$$\alpha = \left(f_1 \cdot 2^{-1} + \dots + f_3 \cdot 2^{-3} + 2^{-4}\right) \cdot \frac{\pi}{4}$$

(2.10)

$$\beta = \left(-\overline{f_4} \cdot 2^{-4} + \dots + f_{13} \cdot 2^{-13}\right) \cdot \frac{\pi}{4}$$

(2.11)

and  $f_4$  is the complement of  $f_4$ .

The goal of the first stage is to perform a rotation by an angle close to  $\alpha+\phi_{LSB}/2$ . To that purpose, the *first rotation* block uses the CORDIC algorithm, described by the following equations:

$$\begin{cases} X_{i+1} = X_i - \sigma_i \cdot 2^{-i} \cdot Y_i \\ Y_{i+1} = Y_i + \sigma_i \cdot 2^{-i} \cdot X_i & i = 1, ..., 4 \\ Z_{i+1} = Z_i - \sigma_i \cdot \tan^{-1} 2^{-i} \end{cases}$$

(2.12)

where  $\sigma_i$  is equal to  $\text{sign}(Z_i)$ . The algorithm starts with:  $X_I = X'_{in}$ ,  $Y_I = Y'_{in}$  and:  $Z_I = \alpha + \phi_{\text{LSB}}/2$ . To simplify hardware implementation, only 4 CORDIC sub-rotations are performed in (2.12), resulting in a rotation by an angle  $\alpha' \neq \alpha + \phi_{\text{LSB}}/2$ . From the CORDIC algorithm properties, it can be easily shown that the absolute value of the residual angle  $Z_{residual} = \alpha + \phi_{\text{LSB}}/2 - \alpha'$  is upper bounded by  $2^{-4}$ . Therefore, by choosing four rotations in the first stage, we have about the same maximum absolute value for both  $Z_{residual}$  and  $\beta$  (see (2.11)). The direction  $\sigma_1$  of the first rotation in (2.12) is fixed ( $\sigma_1 = +1$ ) since  $Z_1 > 0$ . The directions of the remaining rotations ( $\sigma_2, ..., \sigma_4$ ) depend only on  $\alpha$ . These directions, therefore, can be precomputed, by using (2.12), and stored in the lookup table shown in the Fig.2.14. The lookup table is very small, having 3 address bits ( $f_1, f_2, f_3$ ). The residual angle  $Z_{residual}$ , similarly to  $\sigma_i$  values, depends only on  $f_1, f_2, f_3$ . Also  $Z_{residual}$ , therefore, can be stored in the lookup table.

Finally, let us note that the four CORDIC sub-rotations (2.12) amplify the modulus of the input vector by a factor:

$$\rho_1 = \prod_{i=1}^4 \sqrt{1 + 2^{-2i}} \approx 1.16 \tag{2.13}$$

The amplification is inconsequential in many applications [58], [59], [60], [65] and is not compensated in the proposed approach.

#### 2.2.4 Second rotation

In order to complete their operation, the second and third stages of the Hybrid CORDIC architecture rotate the vector  $[X_{T1}, Y_{T1}]$  (the output of the first stage) by an angle:

$$\gamma = Z_{residual} + \beta \tag{2.14}$$

The angle  $\gamma$  is computed by using the  $\pi/4$  multiplier and the adder shown in the Fig.2.14. The  $\pi/4$  multiplier is needed to calculate  $\beta$  from its scaled representation, see (2.11). Since, as we have observed before, the absolute values of  $\beta$  and  $Z_{\text{residual}}$  are both lower than  $2^{-4}$ , the

absolute value of  $\gamma$  is lower than 2<sup>-3</sup>. By representing  $\gamma$  with 11 bits, we have:

$$\gamma = 2^{-3} \left( -g_0 + g_1 2^{-1} + ... + g_{10} \cdot 2^{-10} \right)$$

(2.15)

A phase quantization error in the range [-2<sup>-14</sup>, 2<sup>-14</sup>) is introduced in (2.15). This results in a maximum error at the  $X'_{out}$ ,  $Y'_{out}$  outputs of the DDFSM equal to  $\varepsilon_q$ =1.16·2<sup>-14</sup>. This value is much lower than the weight of the less significant bit at the outputs of the DDFSM (2<sup>-11</sup>).

The angle  $\gamma$  is then split as the sum of two sub-angles:  $\gamma = \gamma_1 + \gamma_2$ , where:

$$\gamma_1 = 2^{-3} \left( -g_0 + g_1 \cdot 2^{-1} + g_2 \cdot 2^{-2} + 2^{-3} \right)$$

(2.16)

$$\gamma_2 = 2^{-3} \left( -\overline{g_3} \cdot 2^{-3} + g_4 \cdot 2^{-4} \dots + g_{10} \cdot 2^{-10} \right)$$

(2.17)

The *second rotation* block is aimed to perform the rotation by the angle  $\gamma_1$ , whereas the rotation by the angle  $\gamma_2$  is assigned to the *final rotation* block.

In the *second rotation* we employ a CORDIC algorithm without the  $Z_i$  computation. The rotation directions  $\tau_i$  are obtained directly by the bits of  $\gamma_1$  as follows:

$$\tau_0 = 2g_0 - 1$$

,  $\tau_i = 2g_i - 1$  for:  $i = 1, 2$  (2.18)

The corresponding CORDIC equations are:

$$\begin{cases}

X'_{i+1} = X'_{i} - \tau_{i} \cdot 2^{-(i+4)} \cdot Y'_{i} \\

Y'_{i+1} = Y'_{i} + \tau_{i} \cdot 2^{-(i+4)} \cdot X'_{i}

\end{cases} i = 0, 1, 2$$

(2.19)

where  $[X'_{\theta}, Y'_{\theta}]$  is the output  $[X_{TI}, Y_{TI}]$  of the first rotation stage, see Fig.2.14.

The actual rotation angle obtained with (2.19) is not exactly the required angle  $\gamma_1$  but is instead an angle  $\gamma_1 \approx \gamma_1$ , given by:

$$\gamma'_1 = \tau_0 \cdot \tan^{-1} \left( 2^{-4} \right) + ... + \tau_2 \cdot \tan^{-1} \left( 2^{-6} \right)$$

(2.20)

From (2.16),(2.18) the angle  $\gamma_1$  can be written as:

$$\gamma_1 = \tau_0 \cdot 2^{-4} + \dots + \tau_2 \cdot 2^{-6} \tag{2.21}$$

As a consequence the *second rotation* block introduces a phase error,  $\phi_{err}$ :

$$\begin{split} \phi_{err} &= \gamma \, '_1 - \gamma_1 \\ &= \tau_0 \cdot \left( \tan^{-1}(2^{-4}) - 2^{-4} \right) + ... + \tau_2 \cdot \left( \tan^{-1}(2^{-6}) - 2^{-6} \right) \end{split} \tag{2.22}$$

With simple manipulations, it is possible to show that  $\varphi_{err}$  is upper bounded by:

$$|\varphi_{\rm err}| < 0.77 \cdot 2^{-13}$$

(2.23)

The phase error of the *second rotation* introduces an error  $\varepsilon_0$  on each component of the DDFSM output. From (2.23),  $\varepsilon_0$  is much lower than the weight of the output LSB (2<sup>-11</sup>).

Like the first rotation block, also the CORDIC rotations (2.19) amplify the modulus of the input vector, by a factor:

$$\rho_2 = \prod_{i=4}^{6} \sqrt{1 + 2^{-2i}} \simeq 1.003 \tag{2.24}$$

Therefore the total amplification factor  $\rho$  is:

$$\rho = \rho_1 \cdot \rho_2 \simeq 1.16 \tag{2.25}$$

## 2.2.5 Final (third) rotation

The *final rotation* block in the Fig.2.14 implements the rotation by  $\gamma_2$ . The operation to be performed by this block can be written as:

$$\begin{cases} X'_{out} = X_{T2} \cdot \cos \gamma_2 - Y_{T2} \cdot \sin \gamma_2 \\ Y'_{out} = X_{T2} \cdot \sin \gamma_2 + Y_{T2} \cdot \cos \gamma_2 \end{cases}$$

(2.26)

This final rotation could also be computed by using the CORDIC algorithm. However, as observed in [71], [72], when the rotation angle is small a complex multiplier is able to reduce the latency and improve the performances.

In our case, the absolute value of  $\gamma_2$  is lower than  $2^{-6}$ . Therefore we can approximate sine and cosine functions in (2.26) as:

$$\sin \gamma_2 \simeq \gamma_2$$

,  $\cos \gamma_2 \simeq 1$  (2.27)

In this way, the final rotation is realized without the need of lookup tables to store sine and cosine values.

The approximation (2.27) introduces an error  $\varepsilon_1$  on the DDFSM outputs  $X'_{out}$  and  $Y_{out}$ . It can be easily shown that this error component is upper bounded by:  $|\varepsilon_1| < 1.16 \cdot 2^{-13}$ .

TABLE 2.7

PERFORMANCES OF THE PROPOSED ARCHITECTURE

| parameter     | value    |               |

|---------------|----------|---------------|

| SFDR          | 93.3 dBc | DDS mode:     |

| Maximum error | 1.01 LSB | (-1,0) input  |

| SNR           | 73.9 dB  | (-1,0) iliput |

| SFDR          | 90.8 dBc | SSB mode:     |

| Maximum error | 1.80 LSB | sine input    |

| SNR           | 70.3 dB  |               |

As shown in the Fig.2.14, we have introduced two rounders in the final rotation stage, to reduce the wordlength of multipliers input. The two rounders introduce an additional error  $\varepsilon_2$  at the output. We have:  $|\varepsilon_2| \le |\gamma_2| \cdot 2^{-7} \le 2^{-13}$ .

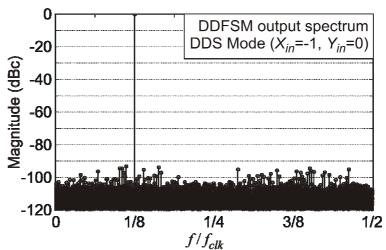

An analytical derivation of the joined effect of all algorithmic and quantization errors is not easy. We performed bit-level simulations, by operating the DDFSM in two modes. In DDS mode  $X_{in}$ =-1 and  $Y_{in}$ =0 so that the circuit generates two quadrature sine wave outputs. In SSB

so that the circuit generates two quadrature sine wave outputs. In SSB mode a sinusoidal input is applied to the DDFSM that operates as a digital up converter with image rejection. The Tab.2.7 summarizes the performances of the developed architecture.

# 2.2.6 Comparison With State Of The Art Approaches

The main advantage of the proposed Hybrid CORDIC architecture is the parallel computation of the rotations directions  $\sigma_i$  and  $\tau_i$ . This computation is performed with a small look-up table, a multiplier by constant and an adder. Therefore simple and effective Carry Save [85] implementation for the datapaths can be used, avoiding the speed penalties due to carry propagation [59].

Previously proposed Carry Save CORDIC architectures require a Z datapath, and also additional carry propagate adders to determine rotations directions [73], [74]. Other techniques do not include carry propagate adders, but require the introduction of extra rotations [75].

The first two CORDIC rotation blocks in our architecture resemble the algorithms proposed in [76]. However, in the partitioned Hybrid CORDIC algorithm of [76] the partitioning and the handling of the rotation angle would require a huge look-up table for its

implementation. On the other hand, the mixed Hybrid CORDIC algorithm, also proposed in [76], does not partition the rotation angle. Therefore its implementation requires in the first stage either a full Z datapath or a look-up table addressed by all the bits of the rotation angle.

The solution of [65] uses two rotation stages. The first one is a CORDIC rotator, while the second one is multiplier based (as originally proposed in [71]). The CORDIC rotator of [65] uses a number of stages comparable to the overall stages used in the first and second block of our architecture. The use in [65] of a single CORDIC rotator, however, requires a lookup table much larger than the one used in our architecture.

The recently proposed DDFSM implementations [62]-[64] use an architecture composed by two multiplier-based rotation stages. These architectures require a total of 8 small-width multipliers. The experimental results shown in the following demonstrate that the Hybrid CORDIC architecture is more effective, especially in terms of power and area occupation.

## 2.2.7 Hybrid Cordic Implementation

The most critical subsystem in the Hybrid CORDIC architecture of Fig.2.14 are the CORDIC stages. In fact the lookup table is very small and can be effectively be synthesized as a random logic. The  $\pi/4$  multiplier requires only the sum of few partial products that can easily be merged with the adder needed to compute  $\gamma$  in a single summation tree.

The final rotation of the Hybrid CORDIC architecture of Fig.2.14 uses multiply-accumulate circuits also realized with a single summation tree. The sign-extension prevention technique [77] has been used to realize the subtraction needed to compute  $X'_{out}$ .

## 2.2.8 Implementation of the Cordic Stages

An innovative architecture has been devised to implement the first and second CORDIC rotation stages. The basic equation to implement the CORDIC stages is:

$$O = X - \sigma \cdot 2^{-i} \cdot Y \tag{2.28}$$

where  $\sigma$  is the direction of the CORDIC sub-rotation, while *i* represents the order of the sub-rotation. The equation (2.28)

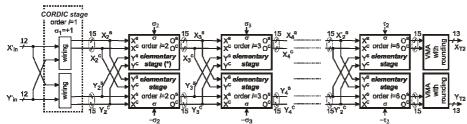

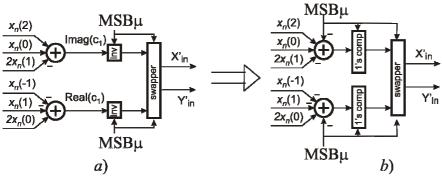

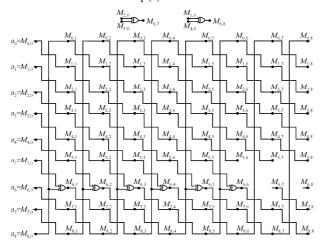

Fig. 2.15. Detailed implementation of the *first* and *second rotation* blocks with Carry -Save arithmetic.

The datapath is built by one wiring block and six CORDIC sub-rotations driven by the directions  $\sigma_2...\sigma_4, \tau_0...\tau_2$ .

implements the X computation in (2.12),(2.19). The Y computation can be easily obtained by swapping X and Y in (2.28) and changing the sign of  $\sigma$ .

Since, in our architecture, the CORDIC rotations directions are efficiently evaluated in parallel, the implementation was performed by using Carry Save arithmetic. Rewriting the (2.28) in Carry Save [85] form, we obtain the main equation to be implemented:

$$O^{s} + O^{c} = X^{s} + X^{c} - \sigma \cdot 2^{-i} \cdot Y^{s} - \sigma \cdot 2^{-i} \cdot Y^{c}$$

(2.29)

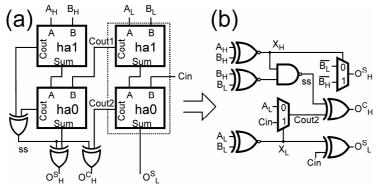

The Fig.2.15 shows the detailed Carry Save datapath of the seven CORDIC stages needed in the architecture of Fig.2.14.

The  $X'_{in}$ ,  $Y'_{in}$  inputs of the circuit of Fig.2.15, are in two's complement representation. The first two blocks in Fig.2.15 implement the first CORDIC sub-rotation with a fixed direction ( $\sigma_1$ =+1). These blocks are also in charge of the conversion from two's complement to Carry Save representation and therefore can be realized by simple wiring and complementations, without additional logic.

The six remaining CORDIC sub-rotations are implemented by using the elementary stages in Fig.2.15. Each elementary stage implements the equation (2.29). The wordlength of the X-Y signals inside the datapath of Fig.2.15 is increased by 2 LSBs (in order to reduce the overall error introduced by the CORDIC elaboration) and by 1 MSB (to avoid overflow).

The two final vector merging adders (VMA), in Fig.2.15, convert the result to two's complement representation. Rounding is also performed in the VMAs to provide the final  $X_{T2}$ ,  $Y_{T2}$  signals with a wordlength of 13 bits.

Fig.2.16. Optimized bit-level implementation in Carry Save arithmetic of

the elementary stage (eq. (2.29)); i is the order of the elementary stage.

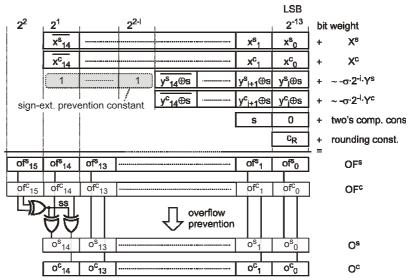

The Fig.2.16 shows the terms to be added to implement (2.29) at the bit level. In this Figure, s is the binary value associated to  $\sigma$  (s=0 if  $\sigma$ =+1 and s=1 for  $\sigma$ =-1). The Fig.2.16 highlights the use of both the sign-extension prevention of [77] and the overflow prevention of [73]. Both techniques allow reducing the circuit complexity with respect to simpler Carry Save approaches [60].

In order to implement the two subtractions of equation (2.29) the bits of  $Y^s$  and  $Y^c$  are XORed with s. Moreover a two's complement constant (the bit equal to s in the column of weight 2·LSB) is also added.

The rounding constant  $c_R$  has been computed in order to minimize the rounding error. For all elementary stages, but the one marked with a star in Fig.2.15, the rounding error is minimized when:  $c_R$ =+1 if s=0 and  $c_R$ =-1 if s=1. Therefore the sum of the two's complement constant and  $c_R$  is equal to 1·LSB. For the elementary stage indicated with a star in Fig.2.15, the optimal rounding constant is zero.

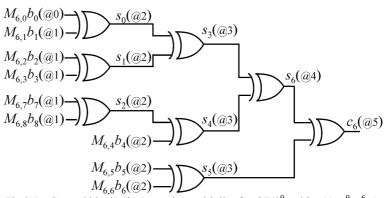

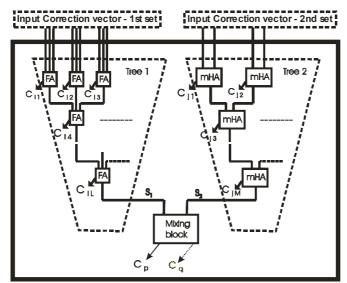

### 2.2.9 Elementary stage implementation

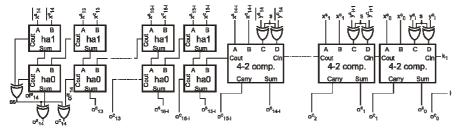

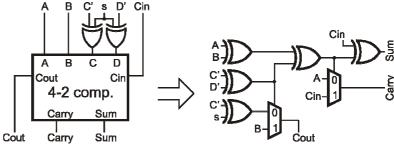

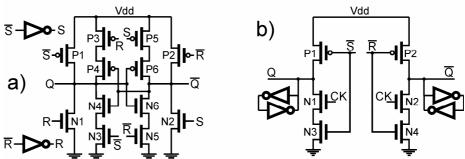

Fig.2.17. Implementation of the *i*-th order *elementary stage* by using 4-2 compressors and half-adders.

For the *elementary stage* marked with a star in Fig.2.15,  $k_1$ =s and  $k_2$ =s.

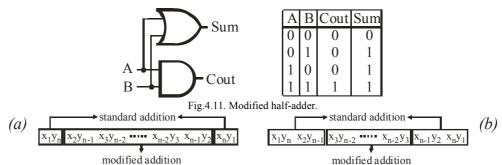

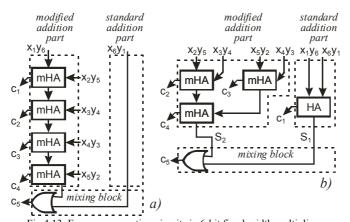

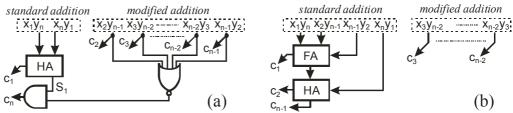

For the other *elementary stages*  $k_1$ =0 and  $k_2$ =1.

The Fig.2.17 shows that the terms of Fig.2.16 can be summed with a single row of 4-2 compressors [78]. Besides these blocks, the circuit requires half adders (ha0 and ha1 for the compression of the MSBs) and XOR gates (for conditional complementing). The ha0 circuits are the "traditional" half adders which compute A+B. The ha1 circuits, instead, compute A+B+1. These blocks allow the summation of the sign-extension prevention constant (see Fig.2.16) without requiring additional hardware.

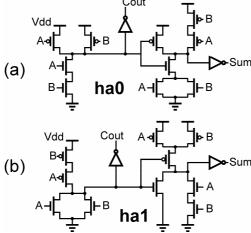

The *ha0* circuit is well known [88]. An effective implementation in CMOS logic is shown in Fig.2.18a. The *ha1* circuit is described by the following equations:

Fig.2.18. Implementation of *ha0* (a) and *ha1* (b) half-adder circuits.

Fig.2.19. Optimal implementation of the first timing critical block in Fig.2.17.

(a) logical function; (b) detailed implementation with simple gates

$$Sum = A \oplus B$$

;  $Cout = A + B$  (2.30)

and is implemented as shown in Fig.7b.

It is interesting to observe, in Fig.2.17, that the employ of the sign-extension prevention allows the use a couple of half adder circuits in place of a single 4-2 compressor, to compute the most significant bits. The most efficient realizations of the 4-2 compressor [79]-[82] requires about 60 MOS, while the couple of half adder circuits, realized as shown in Fig.2.18 require only a total of 28 transistors. The sign-extension prevention technique is, therefore, able to provide a very low circuit complexity. The number of 4-2 compressors decreases with the increase of the order *i* of the stage and, in our approach, this results in a substantial gain in area.

The timing performances of the *elementary stage* shown in Fig.2.17 are limited by two critical paths.

The first timing critical circuit, shown in Fig.2.19a, is composed by a 4-2 compressor with two inputs conditionally complemented. The best available implementations of the 4-2 compressor [81], [82] provide a delay of 3 XOR gates, and include a total of 4 XOR gates plus two multiplexers. Therefore, a straightforward implementation of the circuit of Fig.2.19a requires a maximum delay of four XOR gates.

An optimized implementation of this first timing critical circuit can be obtained by embedding the two XOR gates driven by *s* in the 4-2 compressor. This is not straightforward, since (due to redundancy of the Carry Save arithmetic) different Boolean equations sets exist which provide the same arithmetic function of a 4-2 compressor. We have found that an optimal solution can be obtained starting from the Boolean equations set of the 4-2 compressor introduced by Ghosh *et*

Fig.2.20. Optimal implementation of the second timing critical block in Fig.2.17.

(a) logical function; (b) detailed implementation with simple gates

al. [83], and embedding the XOR gates in the circuit, as shown in the following equations:

$$Cout = (C' \oplus D') \cdot B + (\overline{C' \oplus D'}) \cdot (C' \oplus s)$$

$$Carry = (A \oplus B \oplus C' \oplus D') \cdot Cin + (\overline{A \oplus B \oplus C' \oplus D'}) \cdot A \qquad (2.31)$$

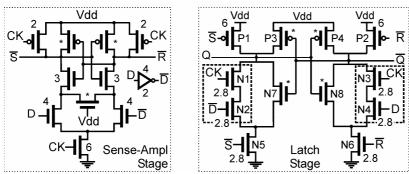

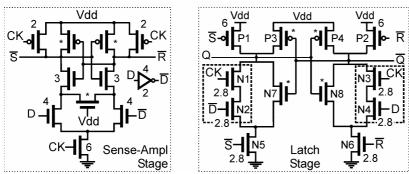

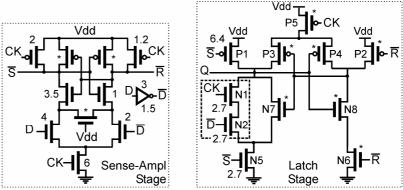

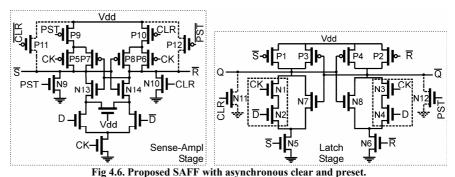

$$Sum = A \oplus B \oplus C' \oplus D' \oplus Cin$$