# **TESI DI DOTTORATO**

UNIVERSITÀ DEGLI STUDI DI NAPOLI "FEDERICO II"

DIPARTIMENTO DI INGEGNERIA BIOMEDICA, ELETTRONICA E DELLE TELECOMUNICAZIONI

DOTTORATO DI RICERCA IN Ingegneria Elettronica e delle Telecomunicazioni

## ANALYTICAL MODELING AND NUMERICAL SIMULATIONS OF THE THERMAL BEHAVIOR OF BIPOLAR TRANSISTORS

## ILARIA MARANO

Il Coordinatore del Dottorato Ch.mo Prof. Giovanni POGGI

Il Tutore Ch.mo Prof. Niccolò Rinaldi

Anno Accademico 2007-2008

# Acknowledgements

I wish to thank all people who helped me during these years giving me the possibility to complete my PhD. First of all, my tutor Prof. Niccolò Rinaldi, whose stimulating suggestions allowed me writing this thesis.

A special thank is for my *pseudo-tutore* Enzo: without his encouragement, patience and comprehension it would have been impossible for me to finish this work. He is a great friend and mentor. Thanks a lot!

I would like also to thank Luigi, Francesco, Marco, Valeria, Nicola, Davide, Lucio, Michele for the pleasant moments that we spent together and their kind words of encouragement.

I'm also very grateful to my parents and sister who always supported me and believed me even when I didn't.

Finally, the greatest thank is for my *husband*, Ciro, for his love and patience. Thanks for having been able to bear my numerous mood swings!

# Index

| Introduction                                                     |                                          |                                                                                                 |    |  |  |  |

|------------------------------------------------------------------|------------------------------------------|-------------------------------------------------------------------------------------------------|----|--|--|--|

| I.1.                                                             | Thermal effects in semiconductor devices |                                                                                                 |    |  |  |  |

| I.2.                                                             |                                          | Thesis contents                                                                                 |    |  |  |  |

| Chapter 1. Isolation schemes in bipolar technology               |                                          |                                                                                                 |    |  |  |  |

| 1.1.                                                             | Trench isolation<br>Silicon-on-insulator |                                                                                                 |    |  |  |  |

| 1.2.                                                             |                                          |                                                                                                 |    |  |  |  |

| 1.3.                                                             | 1                                        |                                                                                                 |    |  |  |  |

| 1.4.                                                             | Thermal issues                           |                                                                                                 |    |  |  |  |

| References                                                       |                                          |                                                                                                 |    |  |  |  |

| Chapter 2. Trench-isolated bipolar transistors on SOI substrates |                                          |                                                                                                 |    |  |  |  |

| 2.1                                                              | Nume                                     | rical analysis                                                                                  | 18 |  |  |  |

|                                                                  | 2.1.1                                    | Heat transfer coefficient evaluation procedures                                                 | 20 |  |  |  |

|                                                                  | 2.1.2                                    | Self-heating thermal resistance evaluation:                                                     |    |  |  |  |

|                                                                  |                                          | adopted approaches and nomenclature                                                             | 21 |  |  |  |

|                                                                  | 2.1.3                                    | Buried oxide thickness variation                                                                | 22 |  |  |  |

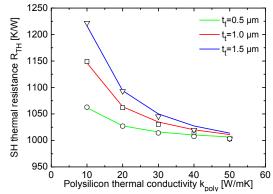

|                                                                  | 2.1.4                                    | Trench depth variation                                                                          | 33 |  |  |  |

|                                                                  | 2.1.5                                    | Trench thickness variation                                                                      | 39 |  |  |  |

|                                                                  | 2.1.6                                    | Silicon island size variation                                                                   | 41 |  |  |  |

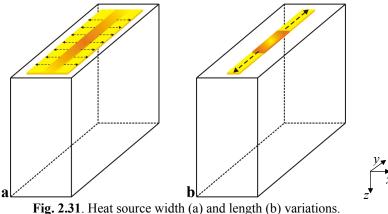

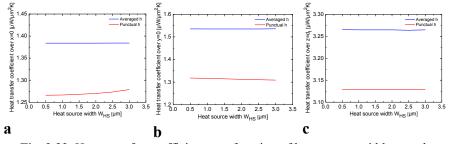

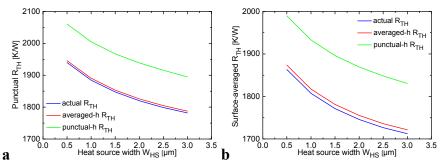

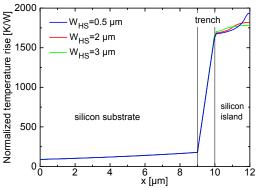

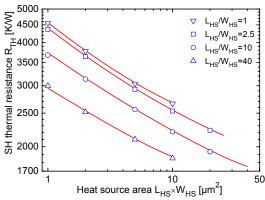

|                                                                  | 2.1.7                                    | Heat source size variation                                                                      | 45 |  |  |  |

|                                                                  | 2.1.8                                    | Variation of the heat source position along                                                     |    |  |  |  |

|                                                                  |                                          | x axis                                                                                          | 48 |  |  |  |

|                                                                  | 2.1.9                                    | Conclusions                                                                                     | 52 |  |  |  |

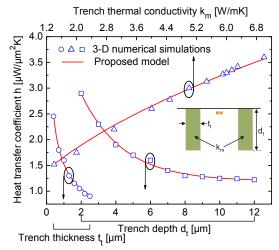

| 2.2                                                              | Heat t                                   | ransfer coefficients empirical model                                                            | 53 |  |  |  |

|                                                                  | 2.2.1                                    | The model                                                                                       | 54 |  |  |  |

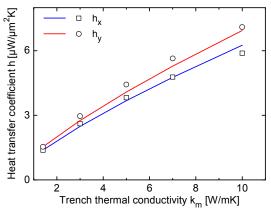

|                                                                  | 2.2.2                                    | Modeling heat transfer coefficients dependence<br>on thermal conductivity of the trench filling |    |  |  |  |

|        |                                                               | 3   |

|--------|---------------------------------------------------------------|-----|

|        | material                                                      | 56  |

| 2.3    | The analytical thermal model                                  | 59  |

|        | 2.3.1 The temperature field                                   | 59  |

|        | 2.3.2 The self-heating thermal resistance                     | 62  |

|        | 2.3.3 Remarks                                                 | 64  |

| 2.4    | Simulation results                                            | 66  |

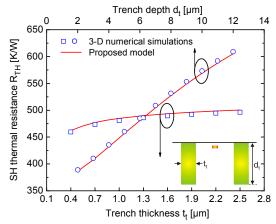

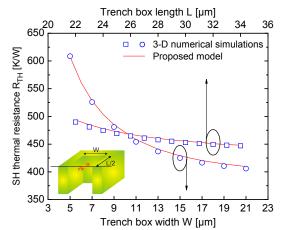

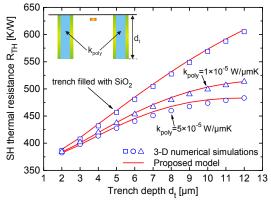

|        | 2.4.1 Self-heating thermal resistance dependence              |     |

|        | on technological parameters                                   | 66  |

|        | 2.4.2 Scaling effects on the self-heating thermal             |     |

|        | resistance                                                    | 69  |

|        | 2.4.3 Temperature distributions evaluation                    | 70  |

| Re     | ferences                                                      | 72  |

| Chante | er 3. Trench-isolated bipolar transistors on bulk             |     |

| Chapte | substrates                                                    | 76  |

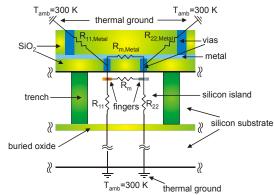

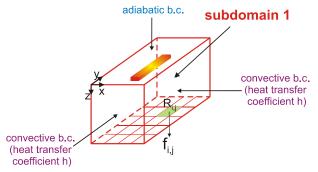

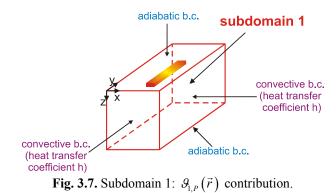

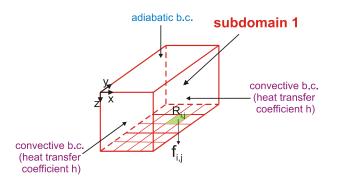

| 3.1    | . Numerical analysis and modeling strategy                    | 78  |

| 3.2    |                                                               | 84  |

| 3.3    | 1                                                             | 86  |

|        | 3.3.1. The temperature field in subdomain 1                   | 87  |

|        | 3.3.2. The temperature field in subdomain 2                   | 96  |

|        | 3.3.3. The temperature field in the overall domain            | 99  |

|        | 3.3.4. The self-heating thermal resistance                    | 99  |

|        | 3.3.5. Remarks                                                | 100 |

| 3.4    | . Simulation results                                          | 105 |

|        | 3.4.1. Analysis of the single-finger DTI transistor           | 105 |

|        | 3.4.2. Comparison with other approaches                       | 109 |

|        | 3.4.3. Thermal design optimization                            | 112 |

| Re     | ferences                                                      | 115 |

| Chapte | er 4. SiGe heterojunction bipolar transistors                 | 119 |

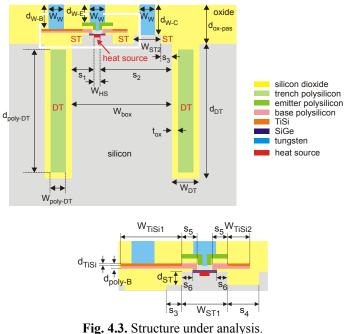

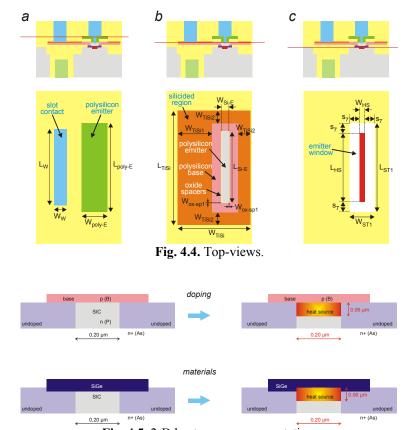

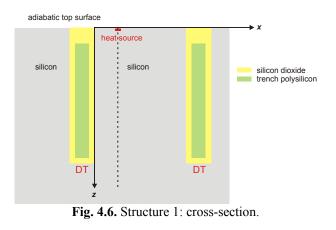

| 4.1    |                                                               | 119 |

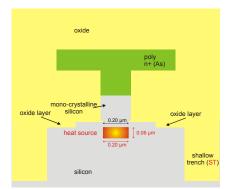

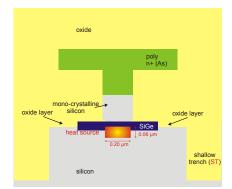

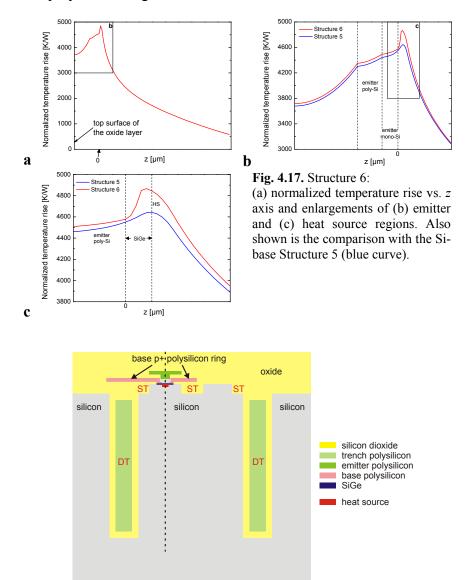

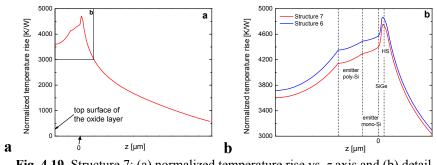

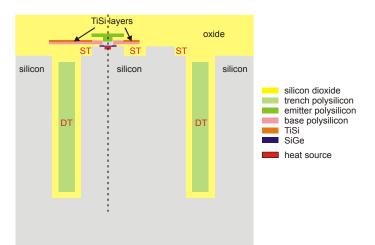

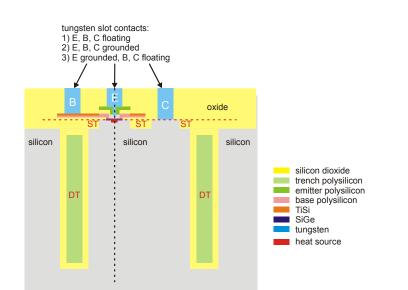

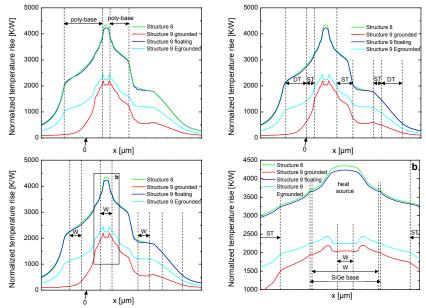

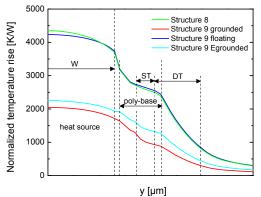

| 7.1    | 4.1.1. The state-of-the-art Infineon SiGe technology          | 119 |

| 4.2    |                                                               | 122 |

| 4.4    | 4.2.1. The reference domain                                   | 123 |

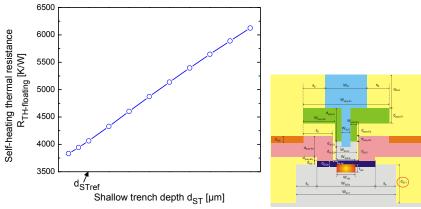

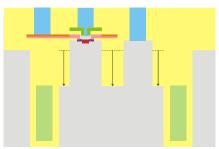

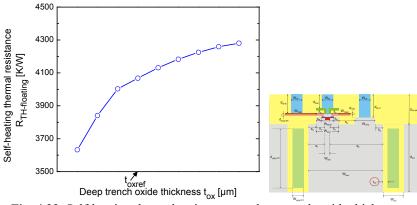

|        | 4.2.1. The reference domain<br>4.2.2. Parametric analyses     | 120 |

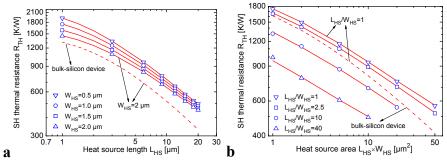

|        | 4.2.2. Parametric analyses<br>4.2.3. Downscaling analysis     | 142 |

|        | 4.2.3. Downscamg analysis<br>4.2.4. Nonlinear thermal effects | 149 |

|        |                                                               | 151 |

|        | 4.2.5. 2-D vs. 3-D analysis                                   | 133 |

|                               | 4.2.6. Numerical vs. experimental results<br>Analytical results<br>aces | 153<br>154<br>156 |  |

|-------------------------------|-------------------------------------------------------------------------|-------------------|--|

| Appendix A. The heat equation |                                                                         |                   |  |

|                               | The heat equation                                                       | 161               |  |

|                               | The boundary conditions                                                 | 163               |  |

| References                    |                                                                         |                   |  |

| Appendix I                    | 3. The steady-state analytical solution of the                          |                   |  |

|                               | heat flow equation: case 1                                              | 166               |  |

| B.1.                          | THS case                                                                | 178               |  |

| B.2.                          | VHS case                                                                | 180               |  |

| Referer                       | nces                                                                    | 182               |  |

| Appendix (                    | C. The steady-state analytical solution of the                          |                   |  |

|                               | heat flow equation: case 2                                              | 183               |  |

| C.1.                          | THS case                                                                | 187               |  |

| C.2.                          | VHS case                                                                | 188               |  |

| Referer                       | nces                                                                    | 190               |  |

| Appendix I                    | ). The steady-state analytical solution of the                          |                   |  |

|                               | heat flow equation: case 3                                              | 191               |  |

| References                    |                                                                         |                   |  |

| Appendix I                    | E. The steady-state analytical solution of the                          |                   |  |

| II.                           | heat flow equation: case 4                                              | 197               |  |

| Referer                       | 1                                                                       | 200               |  |

| Appendix I                    | F. The Kirchhoff transform                                              | 201               |  |

| References                    |                                                                         |                   |  |

# Introduction

#### I.1. Thermal effects in semiconductor devices

Communication and information systems are subject to faster and faster changes. The increasing complexity of electronics systems, requiring higher and higher packing densities and faster circuit speeds, led to an increase in power dissipation and consequently to enhanced self-heating effects. In addition, in order to minimize cross-talk effects and improve high-frequency performances, isolation schemes based on buried oxide layers or deep trench are widely adopted in both bipolar and MOS technologies. These devices are extremely affected by self-heating effects, due to the low thermal conductivity of the buried oxide and the material filling the trench compared to that of silicon. Self-heating effects have become a crucial issue also in heterojunction bipolar transistors (HBTs) due to the high current levels these devices are devised to handle.

Unfortunately, it is well known that thermal effects can affect the reliability and performance of the system so that an exact prediction of the thermal behavior becomes of fundamental importance during device/circuit design. For this purpose an accurate investigation of thermal phenomena must be carried out in order to develop high-performance, low-cost and high-reliability electronic systems for high-frequency applications.

In principle, fully 3-D numerical simulations, which are predictive and allow accounting for all the details of an arbitrarily complex geometry, can be performed.

However, even if numerical simulation tools may reduce expensive technological efforts, the fine discretization requested to achieve satisfying simulation accuracy makes such methods too computationally demanding, thus becoming impracticable when dealing with a large number of transistors. As an alternative, one can resort to high-efficiency analytical approaches, since they require a lower computational cost and can be easily included in electrothermal circuit simulation tools. Unfortunately, this is not a trivial task due to inherent structural complexity of the modern devices.

It is clear that both solutions present some disadvantages so that a proper choice about the option to be adopted in a given problem is very important and complex.

#### I.2. Thesis contents

This thesis deals with the analysis of the thermal behavior of bipolar transistors characterized by isolation schemes (i.e., *deep trench, shallow trench, buried oxide layer*) aimed at improving the high-frequency performance of the devices/circuits. The investigation focuses on three types of bipolar transistors: BJT isolated by deep trench and fabricated on SOI (silicon-on-insulator) substrates (i.e., characterized by a buried oxide layer), BJT isolated by deep trench and fabricated on conventional silicon bulk substrates, HBT SiGe characterized by deep and shallow trenches.

In Chapter 1, a brief introduction to the state-of-the-art isolation schemes is presented.

In Chapter 2, the thermal behavior of deep trench isolated structures on SOI substrates is thoroughly analyzed. Detailed 3-D numerical simulations have been performed to investigate the heat transfer capability of silicon-trenches and silicon-buried oxide interfaces and the impact of all technological and material parameters of interest. It has been shown that the heat transfer phenomena across the silicon island sidewalls can be well approximated by considering simplified convective boundary conditions with uniform heat transfer coefficients. Based on such a result, a novel analytical model has been developed for evaluating the temperature field in a trench SOI structure, which is based on the reduction of the domain under analysis to a silicon rectangular parallelepiped with convective boundary conditions at lateral and bottom faces. An extensive comparison with numerical results proves that the model, that is

entirely predictive, is extremely accurate in the overall parameter range (the accuracy has been demonstrated to lie within 5%) and can be adopted for a fast evaluation of the thermal resistance of a trench SOI device as well as of the temperature gradients within the silicon island surrounded by trenches and buried oxide in order to improve the thermal ruggedness during circuit design.

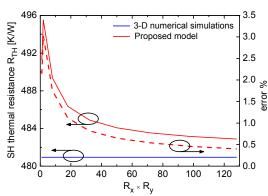

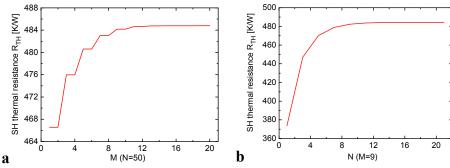

In Chapter 3, a complete and comprehensive analysis of the thermal behavior of trench-isolated bipolar transistors fabricated on conventional bulk-silicon substrates has been carried out. Fully 3-D numerical simulations are performed to analyze the impact of all technological parameters of interest. Based on numerical results, a novel strategy to analytically evaluate the temperature field is proposed, which allows accurately accounting for the heat propagation through the trench and the nonuniform temperature/heat flux distributions over the interface between the silicon trench box and the underlying substrate. The strategy is based on the reduction of the domain under analysis to a simplified structure subdivided into the silicon-only trench box with convective boundary conditions at lateral sidewalls and the silicon substrate. The resulting analytical model is (i) entirely predictive, namely, the thermal behavior of any trenchisolated bipolar transistor can be analyzed starting only from information concerning geometrical and material parameters; (ii) effective, since proper approaches have been chosen to describe the thermal process in both the trench well and the silicon substrate: a few seconds are indeed needed to evaluate a thermal resistance value; and (iii) highly accurate compared to all other predictive models available from the literature: an error <2% is obtained with respect to 3-D numerical simulations in a wide range of values for all technological parameters. As a consequence, the proposed model can be employed for an accurate, yet fast evaluation of the thermal resistance of a trench-isolated device as well as of the temperature gradients within the silicon box surrounded by the trench. Hence, it can be suggested as an effective means for optimizing the thermal design of bipolar transistors fabricated in deep-trench technology with both oxide lined and filled trenches.

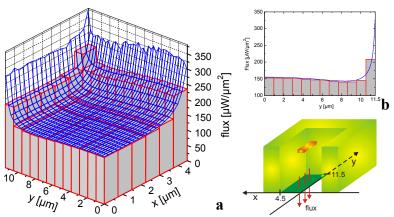

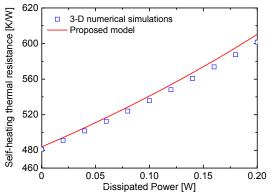

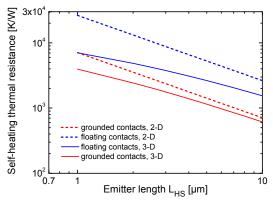

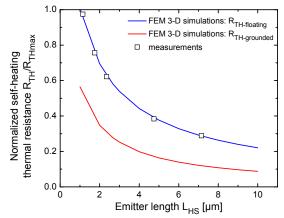

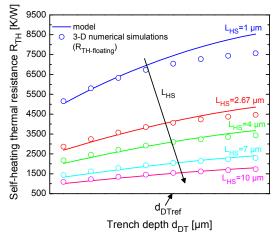

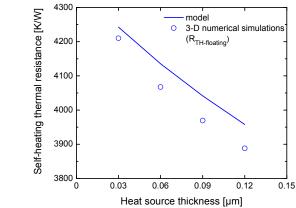

Finally, in Chapter 4, the thermal behavior of SiGe heterojunction bipolar transistors (HBTs) is analyzed. Fully 3-D numerical simulations are performed to analyze the impact on the thermal behavior of all technological elements (e.g., shallow trench, metal slot contacts, deep trench). The numerical results evidenced that the thermal behavior of the overall structure is similar to the one exhibited by a simplified structure in which the heat source is embedded in a bulk silicon substrate and laterally isolated by deep trench. Such a result allows extending to SiGe HBTs the model proposed for trench-isolated bipolar transistors. An accurate parametric analysis allows evaluating the influence on the thermal behavior of all technological parameters of interest (i.e., emitter length, deep and shallow trench depths, heat source thickness, distance between the active region and trench, trench geometry). The scaling effects on thermal resistance are also analyzed as well as the nonlinear effects introduced by the dependence of the silicon and tungsten thermal conductivity on temperature. An extensive comparison with numerical results proves that the model is rather accurate in the overall parameter range (a maximum error of 12% has been relieved).

## **Chapter 1**

# **Isolation schemes in bipolar technology**

A lot of improvements were introduced in bipolar technology since, around 1958, Jack Kilby of Texas Instruments and Robert Noyce of Fairchild Semiconductor independently co-invented the integrated circuit: the epitaxial collector regions above heavily doped buried layers were produced, LOCOS isolation was adopted in place of the junction isolation, narrow base regions were fabricated by means of the implantation of impurities and so on. In order to increase the cutoff frequencies, a reduction of device vertical dimensions was needed. Such aim was reached by realizing arsenic-doped emitters with shallow boron-doped bases. The current gain was further improved by fabricating emitter contacts in polysilicon. It was indeed observed that polysilicon contacts to monocrystalline emitter regions produced gains 4-5 times larger than the ones of comparable metalcontacted emitters. In 1980s, thanks to the plasma-etching processes, the concept of self-alignment was introduced, that allowed reducing significantly the device lateral dimensions and led to the fabrication of the device that represents the state-of-the-art of silicon high-frequency bipolar transistors [1].

Further advances were made by adopting novel isolation techniques, e.g., silicon-on-insulator schemes or shallow/deep trench isolation.

This Chapter briefly discusses the modern isolation techniques with their advantages and drawbacks.

#### **1.1.** Trench isolation

An integrated circuit is based on the concept that many components (passive and active) are fabricated together on the same semiconductor substrate. This target can be achieved only thanks to device isolation.

In an ideal situation, in order to assure that the operation of one transistor does not affect the neighboring ones, each device would be surrounded by a perfect electrical insulator. Unfortunately, in reality this is not possible when dealing with semiconductors.

The earliest type of isolation was introduced by Noyce and it is known as *junction isolation* [2]. The junction isolation is based on the physical property of the silicon PN junction: current cannot flow in a reverse-biased junction. Therefore, the electrical isolation is assured providing the correct voltages to the materials keeping the PN isolation junctions in reverse bias. However, some non-ideal properties affect the PN junction behavior.

- 1. In a reverse-biased junction a current, even if low, always flows. This leakage current increases with temperature and results in a higher power dissipation by the devices that should be isolated, and therefore in a gain reduction.

- 2. There is an intrinsic capacitance associated with a PN junction depending on the reverse voltage applied across it. This capacitance can limit the circuit operating frequency and produce a higher harmonic distortion creating nonlinearities.

- 3. The junction isolation consumes a large amount of silicon area because of lateral diffusions. Furthermore, in high-voltage technologies the space required can become excessively large since the junction isolation size must increase with the applied voltage.

- 4. Finally, if the voltage applied across the reverse-biased junction generates an electric field exceeding the so-called *critical electric field*, the semiconductor will destroy and the current will begin to flow.

Fortunately, around 1980s, the advances in silicon etching technology (i.e., the capability to remove specific silicon areas) allowed realizing the first trenches separating *physically* the devices.

Nowadays many bipolar processes are based on trench isolation to improve packing density [3], reduce parasitic capacitances, minimizing cross-talk interference, and favor latch-up immunity [4]-[7] so as to improve high-frequency device performance.

Shallow trench isolation (STI), also referred to as BIT (Box Isolation Technique), prevents leakage current between adjacent

devices/circuits integrated on the same chip. STI is created during the semiconductor device fabrication process, before realizing active devices. The most important steps of the STI fabrication involve etching a pattern of trenches in silicon, depositing one (or more) dielectric materials to fill the trenches, and removing the excess dielectric using a technique such as chemical/mechanical planarization. STI results in higher packing densities, scaled design rules and lower parasitics that allow reaching higher yields for both CMOS and bipolar circuits. Although demanding on further process steps (i.e., etching and refilling), STI allows reducing the area needed for isolation between circuit elements and consequently the die size, cutting in this way the device cost [8]. However, the shallow trenches are not thick enough to penetrate the epitaxial and buried layers, and do not provide a complete electrical isolation [3]. As a consequence, also the deep trench isolation (DTI) is often adopted, since it provides a further parasitics and crosstalk reduction [6]. As stated before, shallow and deep trenches allow cutting the parasitic capacitances; in particular, they are employed to reduce the base-collector junction capacitance and the collectorsubstrate one, respectively [9], [10] (a capacitance reduction of 4 times can be obtained thanks to the deep trench employment [11]).

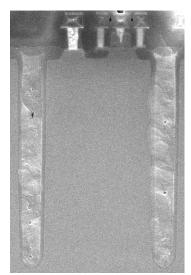

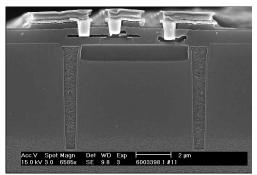

Fig. 1.1 shows the scanning electron microscope (SEM) view of a trench-isolated self-aligned NPN bipolar transistor.

Fig. 1.1. SEM view of a self-aligned NPN transistor. Both shallow and deep trenches are integrated.

The adoption of isolation techniques based on deep trenches allows: a chip area reduction of the order 20-25% with respect to technologies employing standard junction isolation schemes [12]; a decrease by more than 6 orders of magnitude in the parasitic currents injected in the substrate [11]; a current holding increase of 10 times and a reduction in the current gain of the lateral parasitic transistors of about 6 times as compared to trench-free bulk transistors [13].

In conclusion, trench isolation, based on the use of non-conducting materials to isolate the transistors, allows overcoming almost all the non-idealities of junction isolation.

However trench isolation also exhibits some drawbacks.

The trenches are typically filled with an insulator (e.g.,  $SiO_2$ ) or polysilicon lined with  $SiO_2$ . Unfortunately, due to the poor thermal conductivity of the trench-filling materials, the heat flow coming from the active transistor area is mostly confined within the silicon-only region enclosed by the trench before spreading into the substrate, thereby leading to exacerbated thermal issues with respect to bulksilicon transistors of comparable size.

Furthermore, even if the parasitic capacitances are reduced, transistors separated by a deep trench structure are still capacitively coupled to each other and this can affect the electric characteristics of adjacent transistors in dependence of voltage and frequency [8].

#### **1.2.** Silicon-on-insulator

To be fully isolated a transistor should be isolated on all sides.

As concerns the top isolation, in trench-isolated technology, a  $SiO_2$  layer is used (as well as in junction-isolated technology). The bottom isolation, on the contrary, can lead to relevant improvements in the circuit performance.

In the silicon-on-insulator (SOI) technology, the top of the wafer (where the transistors/circuits are located) is electrically insulated by a  $SiO_2$  layer from the silicon substrate. The buried oxide layer can be formed both by a thermal oxidation of the top silicon layer (e.g., [14]) and by an oxygen implantation on a screened oxide silicon wafer (e.g., [15]).

The employment of SOI substrates presents some advantages.

Firstly, a further electrical insulation is provided by the buried oxide [16] that results in a reduction of parasitic capacitances, crosstalk, substrate noise, and latch-up. For this technology, collector-substrate capacitances and collector resistance are lower, resulting in increased operating speeds [17]-[19] (a speed increase of 20-35% is obtained compared to bulk CMOS operating speeds [20]). Furthermore, a reduced power is required to achieve high performance (a 2 to 4 times lower power is needed to operate at the same speed as bulk CMOS [20]). The performance of passive components such as inductors and capacitors, are also improved [21]. In addition, the fabrication process is simplified since an N-type collector/substrate isolation region is no longer needed for the PNP transistor and different voltages may be used on different devices without adding processing steps required for triple wells [20].

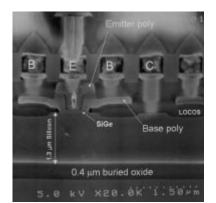

Fig. 1.2 shows the SEM view of a transistor realized on SOI substrate.

Fig. 1.2. SEM view of a SiGe HBT fabricated on SOI substrate.

Even if SOI complementary bipolar technology requires higher initial wafer costs, the reduction in the process complexity and the increase in circuit density fully justify its employment in most technologies.

However, the trend toward smaller and smaller device geometry and higher and higher operating current density leads to a greater sensitivity to thermal effects in bipolar transistors fabricated using the aforementioned technology. The buried oxide exhibits a very low thermal conductivity compared with the silicon one. Therefore the thermal power produced by device junctions can be hardly removed resulting in enhanced self-heating effects that can have deleterious consequences on the reliability and performance of the transistors [22], [23].

# 1.3. Trench-isolated bipolar transistors on SOI substrates

Nowadays advanced technology solutions based on the concurrent adoption of deep trench isolation and buried oxide schemes are increasingly employed due to the need of electrically insulating the active devices from neighboring transistors and substrate. This solution allows overcoming the electrical drawbacks of junction isolation leading to negligible leakage current, reduced parasitic capacitances, and capacitance values independent of the applied voltage variations. In addition, an enhanced immunity to substrate noise and cross-talk are achieved [17], [19], [23].

These features result in faster operating frequencies (since distortion decreases and linearity improves) and lower manufacturing cost (since the isolation size and consequently the die size diminish).

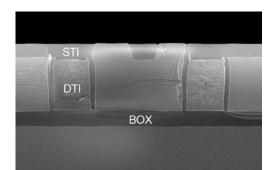

In a trench SOI technology, the active area lies within a silicon island completely enclosed by dielectric layers that ensure the requested full electrical isolation. Fig. 1.3 shows a SEM view of a trench-isolated transistor realized on SOI substrate.

Fig. 1.3. SEM view of a trench-isolated transistor on SOI substrate.

Unfortunately, the poor thermal conductivities of trench materials and buried oxide make the heat removal from the active regions more difficult giving rise to excessively high junction temperatures, if compared to bulk transistors of comparable size embedded in silicononly substrates, which results in performance and reliability degradation.

## 1.4. Thermal issues

As claimed before, due to the poor thermal conductivity of the trench-filling materials and buried silicon dioxide, the heat flow coming from the active transistor area, before spreading into the substrate, is mostly confined within the silicon-only region enclosed by the insulating layers. Therefore the adoption of isolation schemes based on deep trench and buried oxide layer makes the devices noticeably affected by self-heating effects with respect to bulk-silicon transistors of comparable size. This statement will be better clarified in the following.

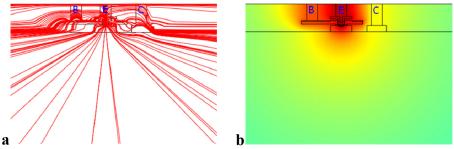

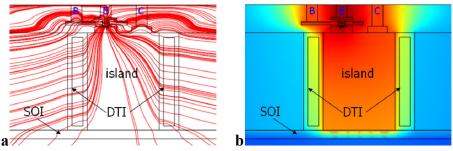

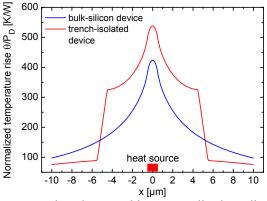

In a bulk-silicon device the heat originated from the active region can flow radially (Fig. 1.4a). Fig. 1.4b shows the corresponding temperature field.

**Fig. 1.4.** Thermal behavior of a bulk bipolar transistor: (a) heat flux lines and (b) temperature field.

In a trench-isolated device the heat flows more hardly through the trench (Fig. 1.5a) so that the temperature reaches higher values in proximity of the heat source (Fig. 1.5b).

**Fig. 1.5.** Thermal behavior of a trench-isolated bipolar transistor: (a) heat flux lines and (b) temperature field.

Finally, in a bipolar transistor characterized by the simultaneous adoption of deep trench an buried oxide layer, no silicon paths are available for the heat removal from the active region, so that the heat flow is mostly confined within the silicon island (Fig. 1.6a). This performance exacerbates electrothermal issues with respect to other less drastic isolation schemes, i.e., based only on either trenches or a buried oxide layer, leading to higher temperature peaks (Fig. 1.6b).

**Fig. 1.6.** Thermal behavior of a trench-isolated bipolar transistor fabricated on SOI substrate: (a) heat flux lines and (b) temperature field.

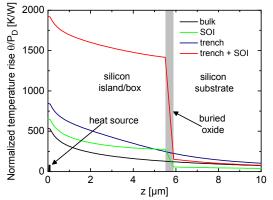

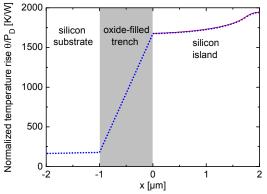

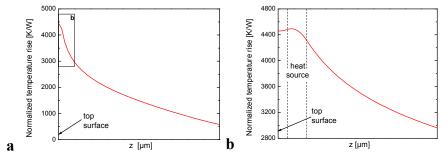

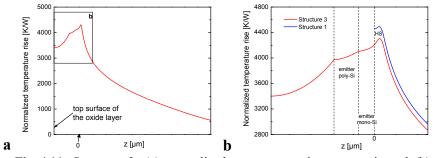

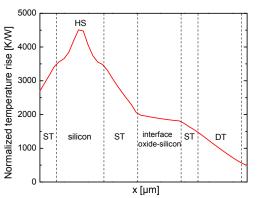

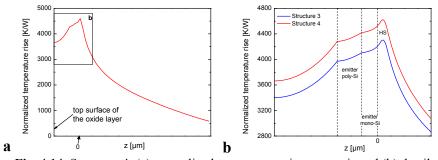

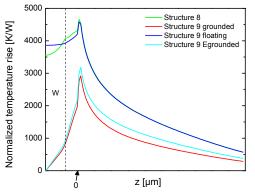

This is evidenced in Fig. 1.7., which illustrates the temperature rise above ambient normalized to dissipated power along a vertical line crossing the active area center for various structures, as evaluated through the commercial 3-D numerical simulator Comsol based on the finite element method [24].

**Fig. 1.7.** Temperature rise above ambient normalized to dissipated power along the *z* axis as obtained by 3-D numerical simulations. An active region of  $0.5 \times 20 \ \mu\text{m}^2$  is considered. The cut is taken through the heat source center. The cases of a bulk-silicon transistor (black line), a pure trench-isolated device (blue), a trench-free SOI structure (green), and a trench-isolated SOI one (red) are compared.

It is shown that the self-heating thermal resistance<sup>1</sup> of the trenchisolated SOI transistor, evaluated on the projection of the heat source center on the top surface, amounts to 1860 K/W, while values of (a) 550, (b) 650, and (c) 850 K/W were obtained by (a) removing both trenches and buried oxide (i.e., considering a conventional bulksilicon device), (b) eliminating only the trenches (i.e., considering a trench-free SOI structure), and (c) removing only the buried oxide (i.e., considering a pure trench bipolar transistor), respectively.

#### References

- [1] Reisch M. High-frequency bipolar transistors: Physics, Modeling, Applications. Springer; 2003.

- [2] Thiel F, and Stibila M. The benefits of trench isolation in high-voltage, high-bandwidth semiconductors: Part I The

<sup>&</sup>lt;sup>1</sup> The self-heating thermal resistance  $R_{TH}$  represents an indicator of the device capability to dispose of heat and it is defined as the temperature rise above ambient normalized to dissipated power:  $R_{TH} = (T_j - T_{AMB})/P_D$ .

technology and the physics of trench isolation. [Online]. Available: http://www.analogzone.com/nett0614.pdf

- [3] Ashburn P. SiGe Heterojunction Bipolar Transistors. John Wiley and Sons; 2003.

- [4] Walkey DJ, Smy TJ, Reimer C, Schröter M, Tran H, Marchesan D. Modeling thermal resistance in trench-isolated bipolar technologies including trench heat flow. Solid-State Electron 2002;46(1):7-17.

- [5] Harame DL, Comfort JH, Cressler JD, Crabbè EF, Sun JYC, Meyerson BS, Tice T. Si/SiGe epitaxial-base transistors – Part II: Process integration and analog applications. IEEE Trans Electron Dev 1995;42(3):469-82.

- [6] Forsberg M, Björmander C, Johansson T, Ko T, Liu W, Vellaikal M, Cheshire A. Shallow and deep trench isolation for use in RF-Bipolar ICs. IEEE ESSDERC Proc 2000:212-5.

- [7] Ohue E, Oda K, Hayami R, Washio K. A 7.7-ps CML using selective-epitaxial SiGe HBTs. IEEE BCTM Proc 1998:97-100.

- [8] Lee SS, Allstot DJ. Electrothermal simulation of integrated circuits. IEEE J. Solid-State Circuits 1993;28(12):1283-93.

- [9] Washio K, Kondo M, Ohue E, Oda K, Hayami R, Tanabe M, et al. A 0.2-µm self-aligned SiGe HBT featuring 107-GHz f<sub>max</sub> and 6.7-ps ECL. IEEE IEDM Proc 1999;557-60.

- [10] Nii H, Yoshino C, Yoshitomi S, Inoh K, Furuya H, Nakajima H, et al. An 0.3-μm Si epitaxial base BiCMOS technology with 37-GHz f<sub>max</sub> and 10-V BV<sub>CEO</sub> for RF telecommunication. IEEE Trans Electron Dev 1999;46(4):712-21.

- [11] Parthasarathy V, Zhu R, Khemka V, Roggenbauer T, Bose A, Hui P, et al. A 0.25µm CMOS based 70V smart power technology with deep trench for high-voltage isolation. IEEE IEDM Proc 2002;459-62.

- [12] De Pestel F, Coppens P, De Vleeschouwer H, Colson P, Boonen S, Colpaert T, et al. Deep trench isolation for a 50 V 0.35 μm based smart power technology. IEEE ESSDERC Proc 2003:191-4.

- [13] Gilbert PV, Crabtree PE, Sun SW. Latch-up performance of a sub-0.5 micron inter-well deep trench technology. IEEE IEDM Proc 1993;731-34.

- [14] Masui S, Kawamura K, Hamaguchi I, Yano T, Nakajima T, and Tachimori M. An analysis of buried-oxide growth in low-dose SIMOX wafers by high-temperature thermal oxidation. IEEE International SOI Conference Proc 1995;154-5.

- [15] Mulcahy C, Biswas S, Kelly I, Kirkwood D, and Collart E. The distribution of boron and arsenic in SOI wafers implementing SIMS. IEEE International Ion Implantation Technology Conference Proc 2002;1-4.

- [16] Leung YK, Kuehne SC, Huang VSK, Nguyen CT, Paul AK, Plummer JD, Wong SS. Spatial temperature profiles due to nonuniform self-heating in LDMOS's in thin SOI. IEEE Trans Electron Dev Let 1997;18(1):13-15.

- [17] Nigrin S, Wilson MC, Thomas S, Connor S, Osborne PH. A complementary bipolar technology on SOI featuring 50GHz NPN and 35GHz PNP devices for high performance RF applications. IEEE International SOI Conference Proc 2002;155-7.

- [18] Sun ISM, Ng WT, Kanekiyo K, Kobayashi T, Mochizuki H, Toita M, et al. Lateral high-speed bipolar transistors on SOI for RF SoC Applications. IEEE Trans Electron Dev 2005;52(7):1376-83.

- [19] Malm BG, Haralson E, Johansson T, Östling M. Self-heating effects in a BiCMOS on SOI technology for RFIC applications. IEEE Trans Electron Dev 2005;52(7):1423-8.

- [20] Simonton R. Special report: SOI wafer technology for CMOS ICs. [Online]. Available:

http://icknowledge.com/threhold\_simonton/soitechnology.pdf

- [21] Mastrapasqua M, Palestri P, Pacelli A, Celler GK, Frei MR, Smith PR, et al. Minimizing thermal resistance and collector-tosubstrate capacitance in SiGe BiCMOS on SOI. IEEE Trans Electron Dev 2002;23(3):145-7.

- [22] Kopp D. An efficient and accurate thermal model of Silicon-On-Insulator (SOI) integrated circuits. Thesis topic, Clarkson University. [Online]. Available:

http://www.clarkson.edu/honors/research/thesis.php

- [23] Ganci PR, Hajjar JJJ, Clark T, Humphries P, Lapham J, Buss D. Self-heating in high performance bipolar transistors fabricated on SOI substrates. IEEE IEDM Proc 1992;417-20.

- [24] Comsol Multiphysics 3.3. User's Guide. Comsol AB, 2007.

#### Chapter 2

# Trench-isolated bipolar transistors on SOI substrates

Nowadays, the demand for increasingly smaller chip sizes and higher operation frequencies results in a growing number of processes making a concurrent use of deep trench isolation and silicon-on-insulator schemes. As stated before, this solution allows electrically insulating the active devices from both neighboring transistors and substrate, which leads to a number of attractive features, e.g., reduced parasitic capacitances, low leakage currents, and enhanced immunity to substrate noise and crosstalk [1]-[4].

Unfortunately, the poor thermal conductivities of trench materials and buried oxide, which surround the active area confining the heat flow coming from it, lead to enhanced self-heating effects with respect to bulk-silicon devices of comparable size. Hence, an accurate prediction of the thermal behavior of these structures is needed in order to optimize their design.

In principle, one can resort to fully 3-D numerical simulations, which allow accounting for all the geometry details. However, they are CPU/memory demanding, thus becoming unviable when the number of transistors becomes considerable. As an alternative, high-efficiency analytical approaches can be pursued, since they require a lower computational cost.

Unfortunately, developing analytical thermal models is not a trivial task due to inherent structural complexity of trench-isolated SOI bipolar transistors. Some analytical approaches have been conceived to evaluate the thermal resistances of *either* trench [5]-[9] *or* SOI structures [5], [10]. On the other hand, analyses that simultaneously account for deep trenches and SOI are rarely encountered in literature, although the trench and SOI combination is increasingly employed in ICs in order to achieve a full electrical

isolation of the active devices [11]-[13]. An estimate of the thermal resistance of a trench-isolated SOI structure can be obtained by considering the parallel of thermal resistances associated with the individual sidewalls and buried oxide layers [5]. However, this approach does not allow evaluating the whole temperature distribution in the silicon island surrounded by insulators. To our knowledge, only an attempt to solve this problem has been made in [14], where the authors develop a physics-based analytical model that describes the thermal process in trench SOI devices under transient conditions. However, the resulting mathematical formulation is based on severe assumptions (e.g., a 1-D heat flux through buried oxide and trenches) that adversely affect its accuracy, thus leading to a rather large discrepancy when compared to 3-D numerical results.

In this Chapter, a thorough investigation of the thermal behavior of trench-isolated devices fabricated on SOI substrates under steady-state conditions is presented. The Chapter is organized as follows.

First, detailed thermal-only 3-D numerical simulations are performed to analyze the influence of all geometrical and material parameters on the temperature distribution as well as the heat removal capability of the interfaces between silicon and insulating layers. It is demonstrated that the interfaces between the silicon island and the surrounding insulated materials exhibit a nonuniform proneness to transfer heat.

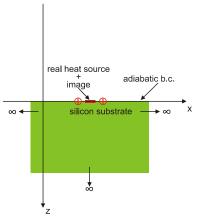

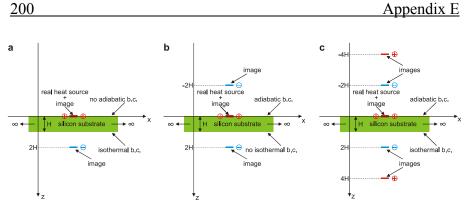

Subsequently, starting from the numerical results, a novel modeling strategy is developed, which involves the replacement of the actual domain with a simplified silicon-only one with proper boundary conditions that allow describing the thermal process. In particular, convective boundary conditions are adopted, which involve a proper choice of the heat transfer coefficients<sup>2</sup> [W/ $\mu$ m<sup>2</sup>K] (also referred to as trench conduction parameters [15]). Therefore empirical expressions for the heat transfer coefficients are derived to account for their dependence upon all relevant parameters.

Afterward, based on the adopted strategy, an analytical model for the thermal resistance of trench SOI structures was developed. The resulting model is fully predictive, i.e., it allows evaluating the

<sup>&</sup>lt;sup>2</sup> The heat transfer coefficient  $[W/\mu m^2 K]$  is defined as the ratio between heat flux and temperature increase above ambient and describes the surface capability to transfer heat [see Eq. (2.2)].

thermal behavior of the structure only from information concerning the corresponding technological details (i.e., geometry and material properties).

Finally, the thermal behavior of a trench SOI structure as a function of all relevant geometry and material parameters is analyzed by means of the model and numerical data. An extensive comparison with 3-D numerical simulations has allowed proving that, despite its simplicity, the model is extremely accurate in a wide range of values for all relevant geometrical and material parameters playing a role. Besides, it requires extremely short simulation times without convergence problems. As a consequence, it can be conveniently used to predict technology-scaling trends as well as to detect temperature gradients within the silicon island.

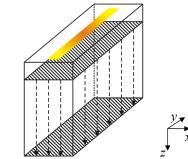

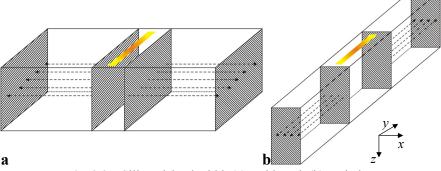

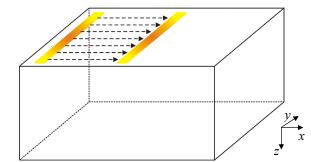

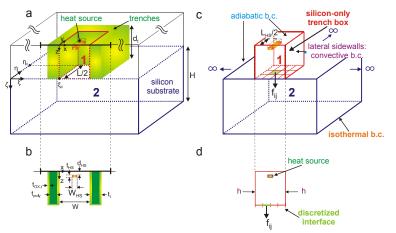

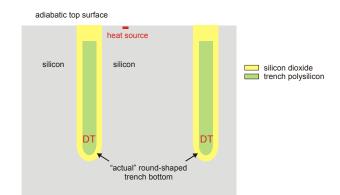

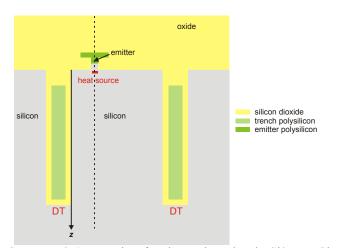

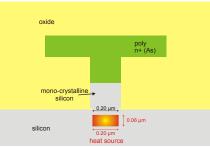

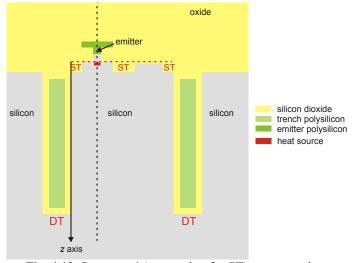

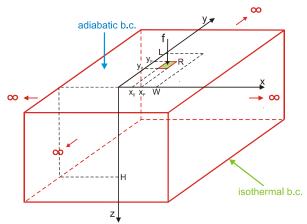

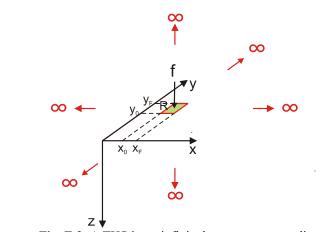

#### 2.1. Numerical analysis

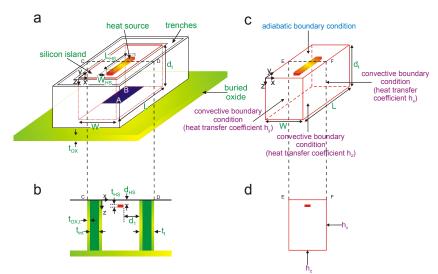

The domain under analysis is shown in Fig. 2.1a and b, and is comprised of a silicon island surrounded by deep trenches and a buried oxide layer, embedded in a 300- $\mu$ m thick silicon substrate, with bottom surface assumed to be in an intimate contact with an ideal heat sink at temperature  $T_{AMB} = 300$  K.

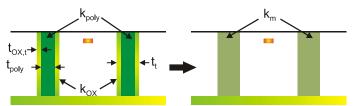

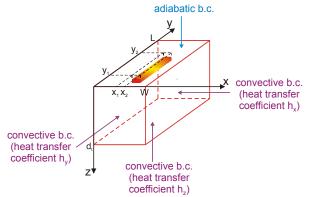

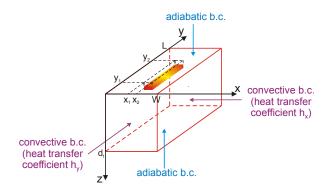

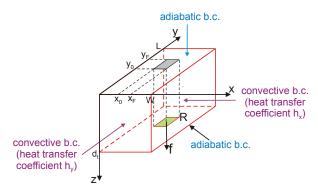

An exact analytical description of the thermal process in a trench SOI structure is prohibitive due to its intrinsic geometrical complexity. For this reason, we have conceived an effective strategy to simplify the problem, which is similar to the approach exploited in [6] for trench-only devices, and can be summarized as follows: the actual domain (Fig. 2.1a and b) is replaced by a silicon-only domain identical to the silicon island with convective boundary conditions<sup>3</sup> at bottom and lateral faces, and adiabatic top surface (Fig. 2.1c and d).

<sup>&</sup>lt;sup>3</sup> A convective boundary condition (also referred to as condition of  $3^{rd}$  kind or Robin condition) imposes a proportionality relationship between heat flux and temperature through the heat transfer coefficient [see Eq. (2.8)] at an assigned surface. It is noteworthy that, despite its nomenclature, the *convective* condition is used to describe a *heat conduction* phenomenon, namely, the heat transfer through the trench sidewalls and buried oxide.

**Fig. 2.1.** (a) Analyzed trench SOI domain and (b) corresponding cross section; (c) simplified silicon-only domain with convective boundary conditions on lateral and bottom surfaces and (d) related cross section.

The proposed approach requires an adequate choice for the values of heat transfer coefficients associated with the convective conditions, which represent tuning parameters to describe the outward flux through the trench and buried oxide sidewalls in the actual structure. This task was accomplished by resorting to an extensive numerical analysis of the trench SOI structure. Such an investigation has been aimed at achieving a better understanding of the thermal behavior and its dependence upon all relevant geometrical and physical parameters, and deeply studying the heat removal capability of trenches and buried oxide. The analysis is carried out as follows.

A reference structure, with parameter values listed in Table 2.1, was defined. The numerical analyses were performed by varying an assigned parameter and keeping all other parameters constant and equal to the reference ones. All geometrical quantities have been varied, namely, the silicon island width/length, trench depth, buried oxide and trench thickness, and position and geometry of the heat source. The variations were chosen within ranges typical of bipolar technologies (see Table 2.1). The heat source region is represented as a rectangular parallelepiped with length and width equal to those of the emitter window, and vertically coinciding with the base-collector

#### 20 Chapter 2. Trench-isolated bipolar transistors on SOI substrates

space charge region. The heat generated by the source is assumed to be due to uniform power dissipation. The trenches have been initially assumed to be entirely filled with silicon dioxide, whose thermal conductivity was chosen to be  $1.4 \times 10^{-6}$  W/µmK (while  $1.4 \times 10^{-4}$  W/µmK was assumed for silicon).

reference variation range parameter description domain [µm] [µm] W silicon island width 4  $2 \div 20$ 22 L silicon island length  $22 \div 40$ trench thickness  $0.5 \div 1.5$ tt 1  $d_t$ trench depth 5.5  $1 \div 10$ buried oxide thickness 0.4 tox  $0.4 \div 1.2$ trench oxide thickness 0.1 \_\_\_\_ t<sub>OX,t</sub> thickness of the trench \_\_\_\_  $t_t - 2t_{OX,t}$ t<sub>poly</sub> polysilicon layer W<sub>HS</sub> heat source width 0.5  $0.5 \div 3$ 20 L<sub>HS</sub> heat source length 9 ÷ 21 heat source thickness 0.05 t<sub>HS</sub> \_\_\_\_ d<sub>HS</sub> heat source depth 0.05 \_\_\_\_ distance between trench  $0.25 \div 4.75$ 1.75  $d_1$ and heat source  $(at W = 10 \mu m)$

Table 2.1

Geometrical parameters of the trench SOI structure.

#### 2.1.1. Heat transfer coefficient evaluation procedures

In order to study the heat transfer properties of the trench and buried oxide sidewalls, we analyze the corresponding heat transfer coefficient h. In fact, as stated before, the heat transfer coefficient describes the surface proneness to transfer heat out of the silicon-only domain (referred to as *silicon island*). For this purpose we followed two different h evaluation strategies:

1 *Punctual h*: in this case the heat transfer coefficient is evaluated as

$$h = \frac{f(x_{P}, y_{P}, z_{P})}{T(x_{P}, y_{P}, z_{P}) - T_{AMB}}$$

(2.1)

where  $f(x_P, y_P, z_P)$  and  $T(x_P, y_P, z_P)$  are the heat flux and temperature in the projection of the MGC<sup>4</sup> of the heat source on the top surface, respectively, and  $T_{AMB}$  is the ambient temperature.

2 Averaged h: in this case the heat transfer coefficient is evaluated as

$$\overline{h} = \frac{\frac{1}{S} \int f(x, y, z) dS}{\frac{1}{S} \int T(x, y, z) dS - T_{AMB}}$$

(2.2)

being *S* the area of the surface at which *h* is associated.

# 2.1.2. Self-heating thermal resistance evaluation: adopted approaches and nomenclature

In our investigation, three approaches are adopted in order to (numerically) evaluate the self-heating thermal resistance  $R_{TH}$ :

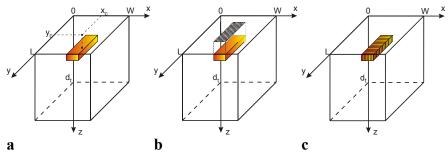

- 1. *Punctual*  $R_{TH}$  approach: the temperature increase above ambient is evaluated on the projection of the MGC of the heat source on the top surface (see Fig. 2.2a).

- 2. Surface-averaged  $R_{TH}$  approach: the temperature increase above ambient is evaluated as an average over a rectangular domain corresponding to the projection of the overall heat source on the top surface (see Fig. 2.2b).

- 3. *Volume-averaged*  $R_{TH}$  approach: the temperature increase above ambient is evaluated as an average over the whole heat source volume (see Fig. 2.2c).

<sup>&</sup>lt;sup>4</sup> MGC is the acronym for mass gravity center (of the heat source). It will be widely used in the following for simplicity.

#### 22 Chapter 2. Trench-isolated bipolar transistors on SOI substrates

**Fig. 2.2.** The different approaches adopted for self-heating thermal resistance evaluation: punctual  $R_{TH}$  (a); surface-averaged  $R_{TH}$  (b); and volume-averaged  $R_{TH}$  (c).

Now, let us introduce the nomenclature adopted for the selfheating thermal resistance numerical evaluation:

- 1. Actual  $R_{TH}$  is the self-heating thermal resistance of the complete structure with trench and buried oxide layer (see Fig. 2.1a).

- 2. *Punctual-h*  $R_{TH}$  is the self-heating thermal resistance of the "fictitious" reduced silicon domain (see Fig. 2.1c). In this case the heat transfer coefficients are calculated from the values of temperature and heat flux evaluated on the projections of the mass gravity center of the heat source on the (lateral and bottom) faces by simulating the overall actual structure.

- 3. Averaged-h  $R_{TH}$  is the self-heating thermal resistance of the "fictitious" reduced silicon domain (see Fig. 2.1c). In this case the heat transfer coefficients are calculated from the averaged temperature and heat flux evaluated on the (lateral and bottom) faces by means of simulations of the overall actual structure.

For each case the self-heating thermal resistance will be evaluated by means of the 3 approaches addressed before.

#### 2.1.3. Buried oxide thickness variation

Let us analyze the influence of the buried oxide thickness on the heat transfer capability of the silicon island sidewalls. In the reference structure the buried oxide thickness amounts to 0.4  $\mu$ m. In the analysis presented in this Paragraph such a thickness spans from 0.4 to 1.2  $\mu$ m (see Table 2.1).

Firstly, the impact on the bottom silicon/buried oxide surface is analyzed.

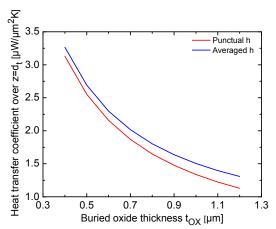

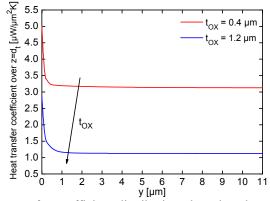

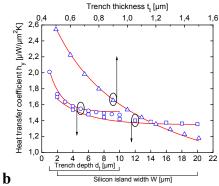

As evidenced in Fig. 2.3, the proneness of the bottom surface to transfer heat away from the silicon island decreases with increasing buried oxide thickness (which is an intuitive result), both in the *punctual* and in the *averaged* case. Besides, an inspection of the figure reveals that the *punctual* h is lower than the *averaged* one. As will be evidenced in the following, this result holds for all the boundary surfaces in almost all the performed analyses.

Fig. 2.3. Heat transfer coefficient over the bottom of the silicon island as a function of buried oxide thickness: both the *punctual* (red line) and *averaged* h (blue) are depicted.

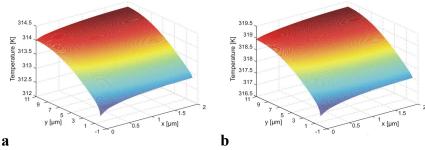

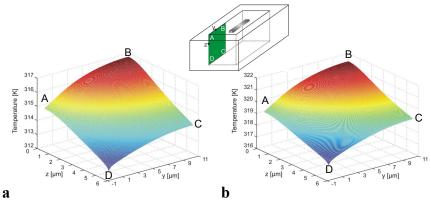

Fig. 2.4a and b illustrate the temperature distribution over the bottom surface (i.e., the interface at  $z = d_t$  between silicon and buried oxide) as obtained through a 3-D FEM simulation of the reference structure ( $t_{OX} = 0.4 \,\mu$ m) and of the structure corresponding to the case of the largest analyzed oxide thickness ( $t_{OX} = 1.0 \,\mu$ m), respectively. A dissipated power density of 20 mW/ $\mu$ m<sup>3</sup> is assumed. Note that due to the inherent symmetry of the structures, only one quarter of the domain has been simulated (see Fig. 2.1a). It is evident that the maximum temperature occurs at the projection of the MGC on the bottom surface (since this is the surface point closest to the heat

source). Furthermore, for  $t_{OX} = 1.0 \,\mu\text{m}$  the temperature values are obviously higher than those corresponding to the 0.4  $\mu\text{m}$  case since the heat is more hardly removed from the silicon domain surrounded by oxide.

**Fig. 2.4.** Temperature distributions over one quarter of the bottom surface of the silicon island as evaluated by numerical simulations for: (a)  $t_{OX} = 0.4 \ \mu\text{m}$ , and (b)  $t_{OX} = 1.0 \ \mu\text{m}$ .

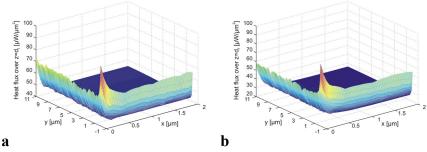

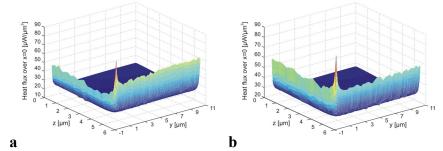

Fig. 2.5 shows the heat flux distribution over the bottom surface for the two previously analyzed cases.

**Fig. 2.5.** Heat flux distributions over one quarter of the bottom surface of the silicon island as evaluated by numerical simulations for: (a)  $t_{OX} = 0.4 \ \mu\text{m}$ , and (b)  $t_{OX} = 1.0 \ \mu\text{m}$ .

As can be seen in Fig. 2.5a, the flux distribution significantly increases in the close proximity of the lateral trenches, while being low (and approximately uniform) far from them. This behavior occurs also by increasing the buried oxide thickness, as evidenced by Fig. 2.5b. Furthermore, a peak is reached on the corner located between trench and buried oxide. This clearly illustrates that this point represents the favorite way for the heat flux to leave the silicon island

within which the active device region is located. It should be noted that the flux distribution over the edge x = 0 (which faces the longest heat source side) is higher than that over the edge y = 0.

As evidenced in Fig. 2.4 and Fig. 2.5, the buried oxide thickness enlargement results in a flux decrease and temperature increase.

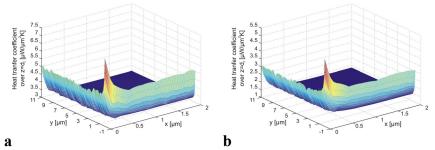

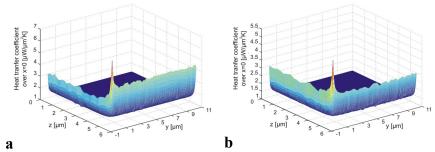

Finally, Fig. 2.6 depicts the *h* distribution over the bottom surface.

**Fig. 2.6.** Heat transfer coefficient distributions over one quarter of the bottom surface of the silicon island as evaluated by numerical simulations for: (a)  $t_{OX} = 0.4 \ \mu\text{m}$ , and (b)  $t_{OX} = 1.0 \ \mu\text{m}$ .

Some observations are in order.

- 1. A noticeably uneven *h* distribution arises: such a parameter exhibits a sharp growth along the edges between lateral trenches and buried oxide with a peak in the corner (point B in Fig. 2.1a), while a *plateau* region with a lower and uniform value occurs far away from the borders, due to the balance between the nonuniform heat flux and temperature distributions. It is therefore evidenced that:

- the heat removal is more effective in correspondence of the boundaries between walls;

- corners represent the preferential way for the heat to leave the silicon island.

- 2. This behavior allows clarifying why the *averaged* h value (which accounts for the h distribution nearby the surface borders) is higher than the *punctual* h (which is located well within the *plateau* region).

- 3. Both the *plateau* values and the border ones decrease with increasing the thickness of the buried oxide. As claimed before, this is a foreseeable behavior, since the bottom surface

#### 26 Chapter 2. Trench-isolated bipolar transistors on SOI substrates

more hardly allows the heat propagation toward the substrate for larger  $t_{OX}$  values.

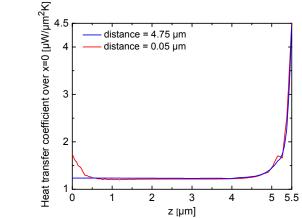

Fig. 2.7 shows the *h* behavior over the bottom interface along a cut taken through the center of the bottom surface for two values of buried oxide thickness  $t_{OX}$ . As can be seen, the surface capability to transfer heat out of the silicon island reduces by increasing  $t_{OX}$ .

**Fig. 2.7.** Heat transfer coefficient distribution along length over the bottom surface of the silicon island for two values of buried oxide thickness; the sharp increase in the close proximity of y = 0 (i.e., the trench sidewall) is apparent. The cut is taken through the center of the surface.

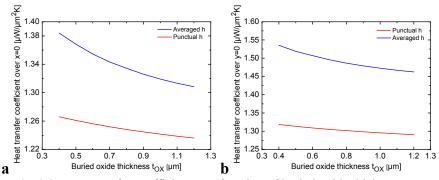

In Fig. 2.8 the *averaged* and *punctual* h on the lateral faces x = 0 and y = 0 are reported (the behavior is identical on the opposite walls due to symmetry).

**Fig. 2.8.** Heat transfer coefficient as a function of buried oxide thickness over lateral sidewalls of the silicon island: (a) x = 0, and (b) y = 0. Both the *punctual* (red lines) and *averaged* h (blue) are depicted.

In both cases, the heat transfer coefficient slightly reduces with increasing the buried oxide thickness (as shown before, a noticeable variation instead occurs for coefficient *h* on the  $z = d_t$  face). Besides, the *punctual h* is lower than the *averaged* one.

Fig. 2.9a and b illustrate the temperature field over the lateral surface x = 0 as obtained through a 3-D FEM simulation of the two structures under analysis (i.e., those with  $t_{OX} = 0.4 \,\mu\text{m}$  and  $t_{OX} = 1.0 \,\mu\text{m}$ , respectively). The maximum temperature occurs on the top surface at  $y = y_c$ . Conversely, the minimum value arises on the bottom surface at y = 0 (which is the farthest point from the heat source MGC). The temperature obviously attains higher values when the buried oxide is thicker ( $t_{OX} = 1.0 \,\mu\text{m}$  in Fig. 2.9b). As we will see, also the heat flux is higher, since the heat flows more easily through the lateral faces than through the bottom surface when the buried oxide thickness increases.

**Fig. 2.9.** Temperature distributions over half of the lateral surface x = 0 (see inset) as evaluated by numerical simulations for: (a)  $t_{OX} = 0.4 \ \mu\text{m}$ , and (b)  $t_{OX} = 1.0 \ \mu\text{m}$ .

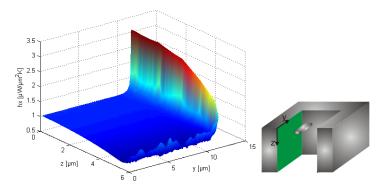

Fig. 2.10 shows the heat flux distribution over the lateral surface x = 0 for the same values of buried oxide thickness.

As can be seen, the flux reaches the maximum value where the temperature is minimum, while being low and uniform far from the oxide walls. Similar results are obtained for the y = 0 surface.

**Fig. 2.10.** Heat flux distributions over half of the lateral surface x = 0 as evaluated by numerical simulations for: (a)  $t_{OX} = 0.4 \,\mu\text{m}$ , and (b)  $t_{OX} = 1.0 \,\mu\text{m}$ .

Fig. 2.11 shows the heat transfer coefficient distribution over the x = 0 surface for buried oxide thicknesses equal to 0.4 µm (Fig. 2.11a) and 1.0 µm (Fig. 2.11b).

**Fig. 2.11.** Heat transfer coefficient distributions over half of the lateral surface x = 0 as evaluated by numerical simulations for: (a)  $t_{OX} = 0.4 \,\mu\text{m}$ , and (b)  $t_{OX} = 1.0 \,\mu\text{m}$ .

The following considerations can be drawn:

- 1. in the *plateau* region (located far from the borders), the heat transfer coefficient values remain almost unchanged, since the features of such a region do not vary in this analysis;

- 2. in a similar fashion, the heat transfer distribution along the trench-trench edge (y = 0) does not change;

- 3. the *h* values along the border between the surface and the buried oxide (i.e.,  $z = d_t$ ) decrease by increasing the buried oxide thickness: as a consequence, the *averaged h* on the

overall surface (also for the "border" values) lowers with increasing  $t_{OX}$ .

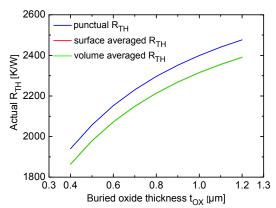

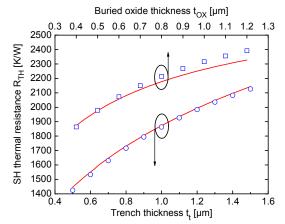

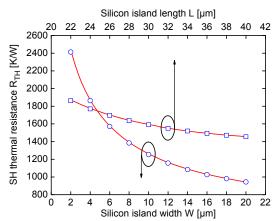

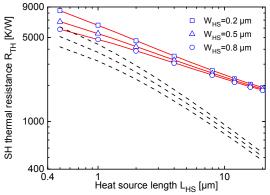

Fig. 2.12 details the behavior of the self-heating thermal resistance  $R_{TH}$  of the real (complete) domain as the buried oxide thickness  $t_{OX}$  increases. As can be seen,  $R_{TH}$  increases with  $t_{OX}$  since a large oxide thickness makes the heat removal from the heat source harder.

**Fig. 2.12.** Self-heating thermal resistance of the actual structure. All the introduced approaches for the evaluation of  $R_{TH}$  are illustrated: punctual (blue line), surface-averaged (red), and volume-averaged (green).

All the introduced approaches (punctual, surface-, and volumeaveraged) are exploited for the evaluation of  $R_{TH}$ . The punctual procedure provides larger values, since the temperature increase over ambient spotted in the projection of the MGC is close to the maximum value in the overall domain. It is noteworthy that the surface and volume-averaged strategies give almost identical results due to the heat source proximity with the top silicon surface and the thin heat source height.

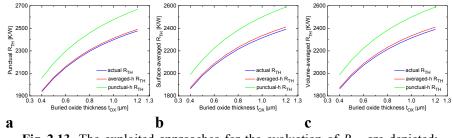

Fig. 2.13 depicts the behavior of the punctual (a), surface- (b), and volume-averaged (c)  $R_{TH}$  as  $t_{OX}$  increases. A comparison is performed between the thermal resistances of (i) the actual structure (blue curves), (ii) the fictitious reduced silicon domain with convective b.c. determined by the *h* values extracted at the MGC projections (green curves), and (iii) the fictitious domain with b.c. established by the *averaged h* (red curves). Let us note that the geometry of heat source and silicon domain surrounded by oxide remains unchanged as the buried oxide thickness changes; as a consequence, the thermal

#### 30 Chapter 2. Trench-isolated bipolar transistors on SOI substrates

behavior of the fictitious structures only depends on the *h* values adopted for the convective b.c.. Fig. 2.13 shows that, independently of the approach adopted to evaluate the self-heating thermal resistance, the *punctual-h*  $R_{TH}$  noticeably overestimates the actual thermal resistance (the error amounts to around 7%), while the *averaged-h*  $R_{TH}$ provides an excellent agreement (a maximum error of 0.7% is found). It will be shown that such a discrepancy reduces when the b.c. influence on the self-heating thermal resistance decreases (i.e., for low  $t_{OX}$  values).

**Fig. 2.13.** The exploited approaches for the evaluation of  $R_{TH}$  are depicted: (a) punctual, (b) surface-averaged, and (c) volume-averaged. For all the approaches the self-heating thermal resistance of the actual structure (blue lines), the *averaged-h* (red), and *punctual-h* (green)  $R_{TH}$  are reported.

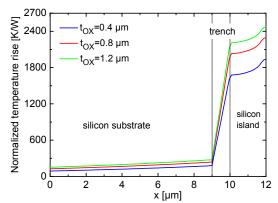

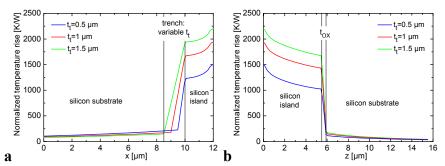

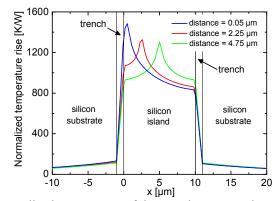

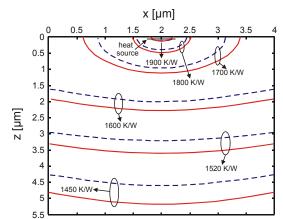

The following figures show the temperature increase over ambient  $\Delta T(x,y,z)$  normalized to dissipated power  $P_D^5$  along the *x*, *y*, and *z* axis as a function of buried oxide thickness.

In the real domain the normalized temperature field can be numerically evaluated in the silicon island, oxide layers (both trenches and buried oxide), and silicon substrate. Conversely, in the fictitious cases (both for the *punctual* and *averaged h*), such a quantity is – obviously – defined only in the silicon island.

The analysis is performed for three  $t_{OX}$  values, i.e., 0.4, 0.8, and 1.2 µm, respectively.

Fig. 2.14 provides the normalized temperature distribution in the actual (complete) domain over the top surface (z = 0) for  $y = y_c$ .

As can be observed, it rapidly decreases over the oxide trench, due to the extremely low  $(1.4 \times 10^{-6} \text{ W/}\mu\text{mK})$  thermal conductivity of the oxide itself. Furthermore, a figure inspection shows that the

<sup>&</sup>lt;sup>5</sup> Such a quantity can be reviewed as a thermal resistance field, and is only dependent upon the geometric and material parameters of the analyzed domain.

normalized temperature distribution tends to be flat nearby the oxide trench interface, that is, such a surface is almost adiabatic.

**Fig. 2.14.** Numerically evaluated normalized temperature distribution of the actual structure along x over the top surface for three values of buried oxide thickness:  $0.4 \ \mu m$  (blue line),  $0.8 \ \mu m$  (red), and  $1.2 \ \mu m$  (green). The cut is taken through the MGC heat source projection on the top surface.

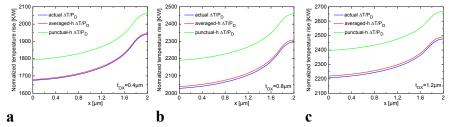

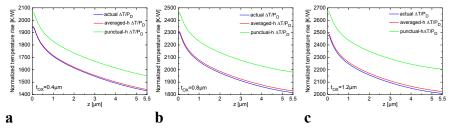

Fig. 2.15 illustrates the normalized temperature field along the *x* axis within the silicon island for the same  $t_{OX}$  values (0.4, 0.8, and 1.2 µm). For each thickness value, a comparison is performed between the normalized temperature fields of (i) the actual structure (blue curves), (ii) the fictitious reduced silicon domain with convective b.c. determined by the *h* values extracted on the MGC projections (green curves), and (iii) the fictitious domain with b.c. established by the *averaged h* (red curves).

**Fig. 2.15.** Normalized temperature fields along *x* over the top surface for three values of buried oxide thickness: (a)  $0.4 \,\mu\text{m}$ , (b)  $0.8 \,\mu\text{m}$ , and (c)  $1.2 \,\mu\text{m}$ . The temperature is evaluated numerically by 3-D FEM simulations: for the actual structure (blue lines), through the *averaged-h* approach (red), and the *punctual-h* one (green). The cut is taken through the projection of the MGC of the heat source on the top surface.

#### 32 Chapter 2. Trench-isolated bipolar transistors on SOI substrates

As can be observed, the *punctual-h* normalized temperature rise significantly overestimates the actual one, while the *averaged-h* temperature provides an admirable agreement also in these cases. Note that the discrepancies between the fictitious *punctual h* and *averaged* h cases with the actual ones are almost independent of the  $t_{OX}$  value.

3-D numerical simulations also proved that the normalized temperature behavior along the y axis is quite similar to the one along the x axis.

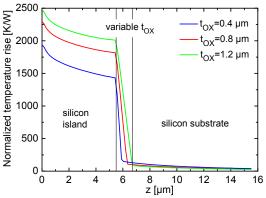

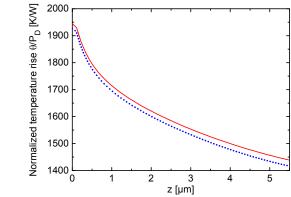

Fig. 2.16 provides the normalized temperature distribution in the actual domain along *z* over a straight line that crosses the MGC as evaluated through 3-D numerical simulations. An insight into the normalized temperature behavior within the silicon substrate reveals that the thinner  $t_{OX}$ , the higher the temperature distribution, since the heat spreads more effectively toward the substrate itself.

**Fig. 2.16.** Numerically evaluated normalized temperature distribution of the actual structure along *z* through the MGC of the heat source for three values of buried oxide thickness:  $0.4 \,\mu\text{m}$  (blue line),  $0.8 \,\mu\text{m}$  (red), and  $1.2 \,\mu\text{m}$  (green).

Fig. 2.17 illustrates once more the normalized temperature field along the *z* axis within the silicon island for  $t_{OX}$  equating 0.4, 0.8, and 1.2 µm, respectively. All considerations are similar to those expressed for the behavior along the *x* axis.

**Fig. 2.17.** Normalized temperature fields along *z* through the MGC of the heat source for three values of buried oxide thickness: (a)  $0.4 \,\mu\text{m}$ , (b)  $0.8 \,\mu\text{m}$ , and (c)  $1.2 \,\mu\text{m}$ . The temperature is evaluated numerically by 3-D FEM simulations: for the actual structure (blue lines), through the *averaged-h* approach (red), and the *punctual-h* one (green).

## 2.1.4. Trench depth variation

Now, let us analyze the influence of the trench depth on the heat transfer capability of the silicon island sidewalls.

In the reference structure the trench depth (i.e., the depth of the interface between silicon island and buried oxide) amounts to  $5.5 \,\mu\text{m}$ . In this investigation such a quantity spans from 1.0 to  $10 \,\mu\text{m}$  (see Fig. 2.18)

Fig. 2.18. Trench depth variation in the simplified domain.

It is to be noted that – contrarily to the former analysis – the area of the surfaces corresponding to x = 0 and y = 0 varies (that is, it increases with increasing the trench depth). By converse, the area of the surface  $z = d_t$  ( $d_t$  changing from 1.0 to 10 µm) remains constant.

As concerns the lateral sidewalls, numerical simulations evidenced that:

#### 34 Chapter 2. Trench-isolated bipolar transistors on SOI substrates

- $\succ$  for any  $d_t$ :

- 1. the maximum temperature is reached on the MGC projection, while the minimum is located in correspondence of the corners between trench and buried oxide layer;

- 2. the heat flux increases toward the surface boundaries (particularly high values are reached at the interface with the buried oxide), whereas it is low and almost uniform far from such boundaries;

- 3. the heat transfer coefficient rapidly grows nearby the wall boundaries reaching a maximum where the temperature is minimum (i.e., at trench-buried oxide corners), while being constant elsewhere. Again, this *plateau* can be explained by considering that, far from the edges, the surface exhibits everywhere uniform features, and, therefore, an uniform proneness to transfer heat;

- $\triangleright$  as the trench becomes deeper (i.e.,  $d_t$  increases):

- 1. the temperature values diminish due to the larger silicon volume surrounded by oxide that facilitates the heat spreading;

- 2. the heat flux distribution reaches lower values, since the silicon domain enlarges and the outgoing heat for unit area decreases;

- 3. the *plateau* value of the heat transfer coefficient (which coincides with the *punctual h*) remains unchanged, nearly independent of the trench depth, since the features of the "internal" wall portion do not vary;

- 4. the *h* values along the borders are almost constant, since also the border features do not change;

- 5. the area of the regions nearby the borders where coefficient *h* rapidly increases remains unchanged.

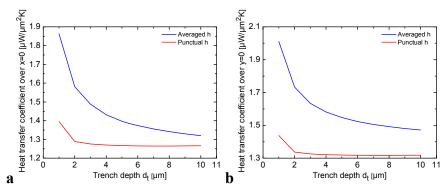

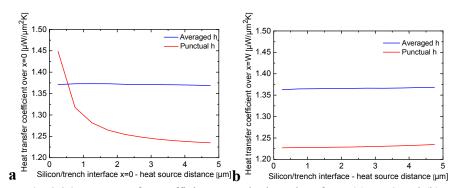

On the basis of these observations, we can easily explain the *punctual* and *averaged* h behavior (red and blue lines in Fig. 2.19a and b, respectively) of the heat transfer coefficient over lateral sidewalls of the silicon island as a function of trench depth.

**Fig. 2.19.** Heat transfer coefficient as a function of trench depth over lateral sidewalls of the silicon island: (a) x = 0, and (b) y = 0. Both the *punctual* (red lines) and *averaged h* (blue) are depicted.

As can be seen:

- the *averaged h* decreases with increasing trench depth (rapidly for low depth values and slowly for high ones) and tends to the *plateau* value; the region where *h* sharply increases is indeed characterized by same area and coefficient values, while the *plateau* area enlarges and plays a more important role;

- 2. the *punctual h*, on the contrary, remains almost unchanged over the whole trench depth range;

- 3. also in this analysis, the *punctual h* is lower than the *averaged* one, even if the discrepancy reduces for large trench depth values.

As concerns the bottom surface  $(z = d_t)$ , numerical simulations evidenced that:

- the maximum temperature is located on the MGC projection (i.e., the center of the silicon island/buried oxide interface), while the minimum occurs in the corner between trench and buried oxide layer;

- 2. the flux is larger on the surface boundaries while being low and almost constant far from them;

- 3. with increasing trench depth, the silicon island volume enlarges so that the temperature peak lowers;

- 4. the heat transfer coefficient distribution remains almost identical on the overall surface as trench depth changes, since

#### <u>36 Chapter 2. Trench-isolated bipolar transistors on SOI substrates</u>

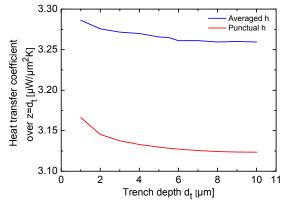

both area and features of the bottom surface are insensitive to buried oxide depth and consequently also the proneness of the surface itself to transfer heat outside does not vary. Therefore both *punctual* and *averaged* h are expected to be almost constant over all the range of trench depth as substantiated by Fig. 2.20.

Fig. 2.20 shows the *punctual* and *averaged* h behavior as a function of trench depth over the bottom surface (silicon/buried oxide interface).

It can be plainly seen that:

- 1. also in this analysis, the *averaged h* is larger than the *punctual* one;

- 2. the *punctual* h raises for small trench depths. This can be intuitively explained as follows: when the bottom interface is extremely close to the heat source bottom, a localized "hill" in the h distribution arises over the heat source projection on the bottom surface and the hill peak increases with lowering trench depth (and, therefore, reducing the vertical spacing between heat source and bottom interface).

Fig. 2.20. Heat transfer coefficient as a function of trench depth over the bottom surface of the silicon island. Both the *punctual* (red line) and *averaged* h (blue) are depicted.

An interesting phenomenon was noted as the trench depth increases. Let us consider  $d_t = 10 \,\mu\text{m}$ . Fig. 2.21 depicts the heat flux distribution over the lateral sidewall x = 0 of the silicon island.

**Fig. 2.21.** Heat flux distribution over half of the lateral surface of the silicon island x = 0 as evaluated by numerical simulations for  $d_t = 10 \ \mu m$ .

As one can see, far from the lateral and bottom borders, the heat flux distribution is not uniform any longer (there is no *plateau* region), but decreases with increasing distance from the top surface. This mechanism can be explained as follows: the heat generated from the active device (which is located in the close proximity of the top surface) reaches more easily the lateral sidewalls that are nearer to the heat source itself.

As concerns the heat transfer coefficient distribution, the usual expected behavior is detected: h sharply increases nearby the wall borders (reaching a maximum in the corner), while being constant elsewhere.

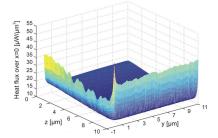

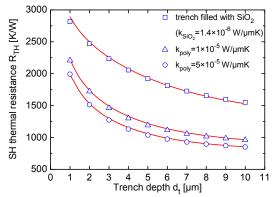

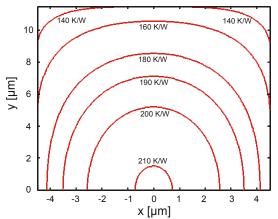

Fig. 2.22 shows the behavior of the self-heating thermal resistance  $R_{TH}$  of the actual domain as the trench depth  $d_t$  increases.

**Fig. 2.22.** Self-heating thermal resistance of the actual structure vs. trench depth. All the introduced approaches for the evaluation of  $R_{TH}$  are depicted: punctual (blue line), surface-averaged (red), and volume-averaged (green).

37

As can be seen,  $R_{TH}$  reduces with  $d_t$  since the silicon domain becomes larger, thus making the heat removal from the region surrounding the heat source easier.

All the approaches (punctual, surface-, and volume-averaged) are exploited for the evaluation of  $R_{TH}$ . Also in this analysis:

- 1. the punctual  $R_{TH}$  provides larger values than the other ones, since the temperature  $\Delta T$  at the MGC projection is close to the maximum  $\Delta T$  value in the overall domain;

- 2. the surface- and volume-averaged  $R_{TH}$  exhibit almost identical values. For this reason in the following investigations only the surface-averaged  $R_{TH}$  will be analyzed.

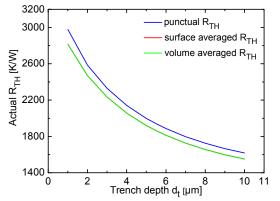

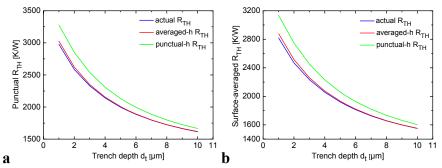

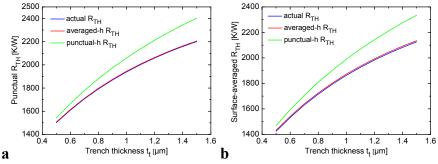

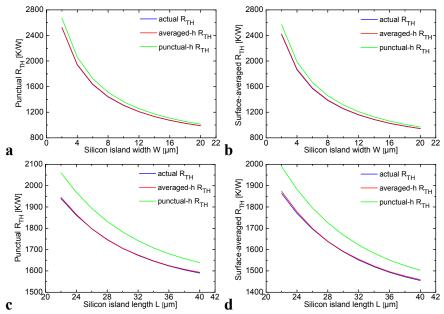

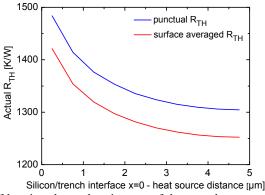

Fig. 2.23 depicts the behavior of the punctual (a) and surfaceaveraged (b)  $R_{TH}$  as  $d_t$  increases. A comparison is performed between the thermal resistances of (i) the actual structure (blue curves), (ii) the fictitious reduced silicon domain with convective b.c. determined by the *h* values extracted in the MGC projections (green curves), and (iii) the fictitious domain with b.c. established by the *averaged h* (red curves).

**Fig. 2.23.** The exploited approaches for the evaluation of  $R_{TH}$  are depicted: (a) punctual, and (b) surface-averaged. For all the analyzed approaches the self-heating thermal resistance of the actual structure (blue lines), the *averaged-h* (red), and *punctual-h* (green)  $R_{TH}$  are reported.

As can be seen, the *punctual-h*  $R_{TH}$  significantly overestimates the actual thermal resistance for low/medium trench depth values, while the *averaged-h*  $R_{TH}$  provides an excellent agreement. However, as lucidly discussed before, the *averaged h* approaches the *punctual h* for deeper trenches. As a consequence, adopting *punctual h* boundary conditions for the fictitious case for relatively deep silicon islands does not lead to significant inaccuracy any longer.

# 2.1.5. Trench thickness variation

Let us investigate the effect of the trench thickness on the device thermal behavior. In the reference domain, the trench thickness amounts to 1  $\mu$ m. In this analysis such a thickness spans from 0.5 to 1.5  $\mu$ m.

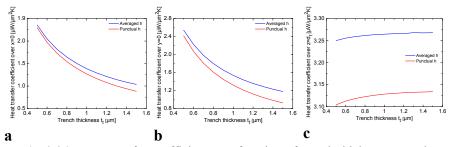

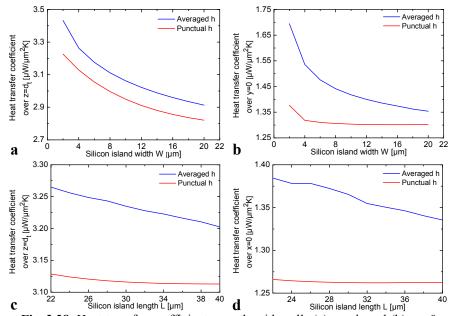

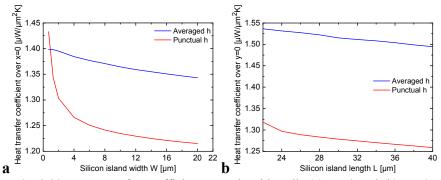

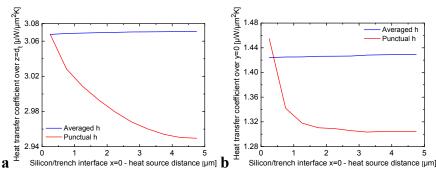

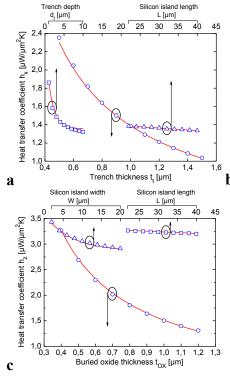

Fig. 2.24 details the *h* behavior over the x = 0, y = 0 and  $z = d_t$  walls, respectively.

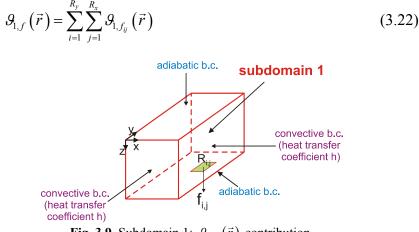

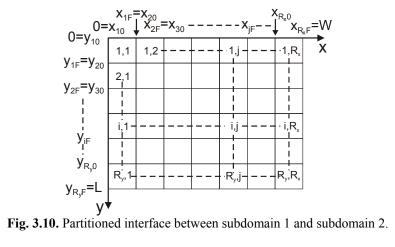

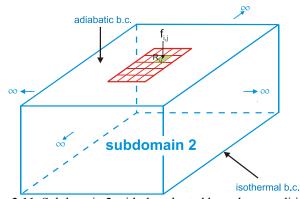

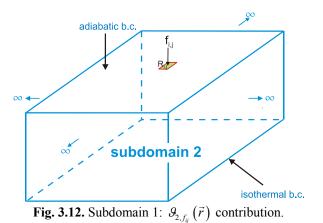

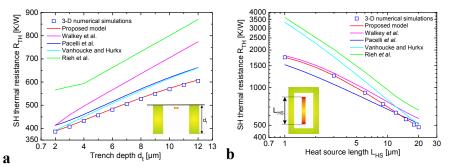

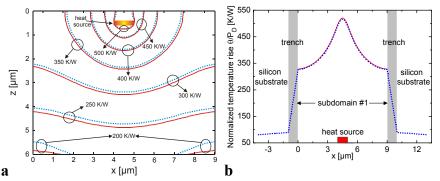

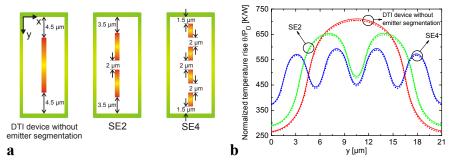

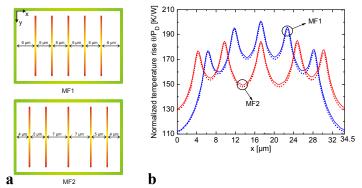

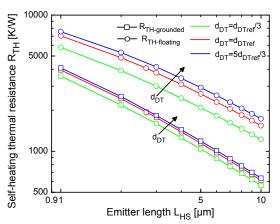

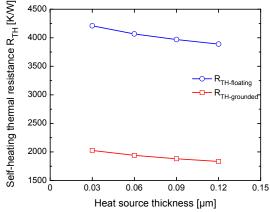

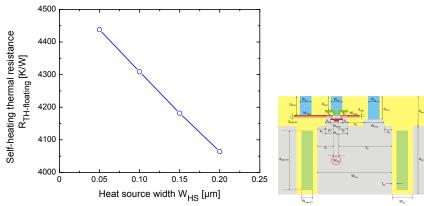

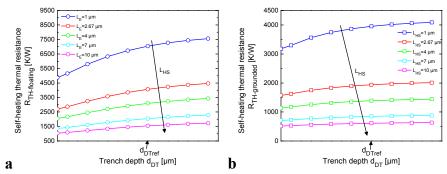

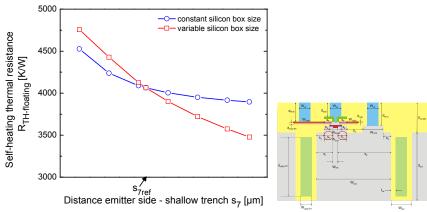

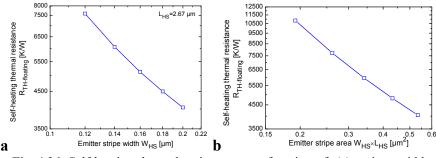

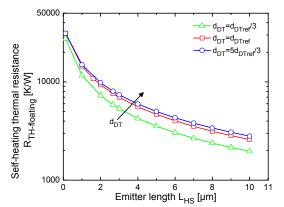

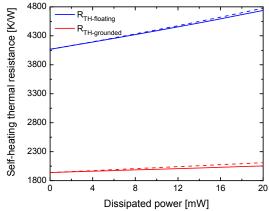

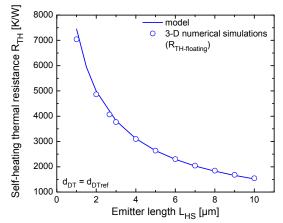

**Fig. 2.24.** Heat transfer coefficient as a function of trench thickness over the silicon island sidewalls: (a) x = 0, (b) y = 0, and (c)  $z = d_t$ . Both the *punctual* (red lines) and *averaged h* (blue) are depicted.